#### CHANDIGARH COLLEGE OF ENGINEERING AND TECHNOLOGY

(Government Institute under UT Administration | Affiliated to Panjab University, Chandigarh)

चंडीगृह अभियान्त्रिकी एवं प्रौद्योगिकी महाविद्यालय (संघ राज्य क्षेत्र प्रशासन के अधीन सरकारी संस्थान। पंजाब विश्वविद्यालय से संबद्ध, चंडीगृह

#### **DIGITAAL NOTES**

Course Code: EC-103 and EC-307

**Subject: Introduction to Electronics and Electronic Devices and Circuits**

B.E: 1st-YEAR and 2nd-YEAR

Name of faculty: Dr. Anil Kumar Vaghmare

#### CHANDIGARHCOLLEGEOF ENGINEERING AND TECHNOLOGY (DEGREE-WING)

Government Institute under Chandigarh (UT) Administration, Affiliated to Panjab University, Chandigarh Sector-26, Chandigarh.PIN-160019

Temperature (in K) LECTURE-1

DR ANIL KUMAR VAGHMARE (1) Absolute temperature: - CCET Degree Wing: OK = -273°C -> Reference temperature -> Below it no temperature exist and no device work at this temperature.

(11) Room temperature: -

300K = 27°C (Never constart)

But if in problem temperature is not given take it BOOK

(III) Ambient Temperature (TA):-

290K = 17°C -> Sworounding temperature

All common esyestem deals with TA 9: - SNR,

Temperature Conversion :-

Temperature in °C = Temperature in kelvin

=> Temperature in Kelyin = Temperature + 273

OK = K - Latest notation.

old notation

-> Hz or cycles/sec

Latest 1

old notation. Notation .

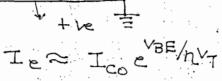

#### Thornal Voltage!

- -> denoted by v7 or V+ or V+h

- -> voltage equivalent of temperature

$$V_T = \overline{KT}$$

volts

T = Temperature in kelvin 9 = charge = 1.6 × 10-19 c K = Boltzman's constant

#### Boltzman's Constant: -

$$K = 1.381 \times 10^{-23} \cdot \text{J/°K}$$

$K = 8.62 \times 10^{-5} \text{ eV/°K}$

$$V_T = \frac{T}{11600}$$

volts

· VT XT

$$A+T=OK$$

$V_T=O$

$$A+T = 300K$$

$_{9}V_{T} = 300 = 0.02568 \text{ volts}$

- → For large variation in temperature (0-300 k) there will be small variation in thermal voltage (6-26 mV)

- The estandard room temperature corresponds to a voltage of 26 mV

(

-> Semiconductor devices are osensitive to temperature very much

#### Electron Volt (eV): -

(1)

۹

(3)

\*

(3)

4

(1)

3

3

9

- electronics.

- -> very small compare to Joule glass tube

- of 1 v

- -> Air is perfect insulator

- -> Vacuum is a conductor

cg:- vacuum tube, picture tube, CRT

- -> Relative peremittivity Ex (aix) = 1 (Slightly 21)

Ex (vacuum) = 1

- $= 1.6 \times 10^{-19} \text{ C} \times 1 \text{ Volts}$   $= 1.6 \times 10^{-19} \text{ C} \cdot \text{Volt}$   $= 1.6 \times 10^{-19} \text{ C} \cdot \text{Volt}$

- > 17 energy can't applied to E's bec. of very less capacity

$$KE = \frac{1}{2}mv^2 J$$

$PE = 9 V J$

gained by the electron or potential energy lost by the electron

in terms of applied voltage (V)

## Electric field Intensity:

- -> Also known as field gradient or field intensity or field

- → denoted by & or E

$$\varepsilon = -\frac{dV}{dx}$$

V/m

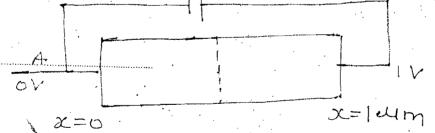

oues!- considering a uniform semiconductor

bar

Find field intensity at the centre of bour and at the end of B.

5017:- (1) Field intensity at the centre of bour

$$|\xi|_{c} = \frac{|V_{c}|}{|x_{c}|} = \frac{|0.5V|}{|0.5\times|0^{-6}|} = \frac{|0.6V|m}{|x_{c}|}$$

(11) Field intensity at the end of B  $16|_{B} = \frac{1V_{B1}}{x_{B}} = \frac{1V}{1\times 10^{-6}} = 10^{6} \text{ m}$

$$(111) |E|_{A} = \frac{|V_{A}|}{x_{A}} = \frac{0}{0} = 222$$

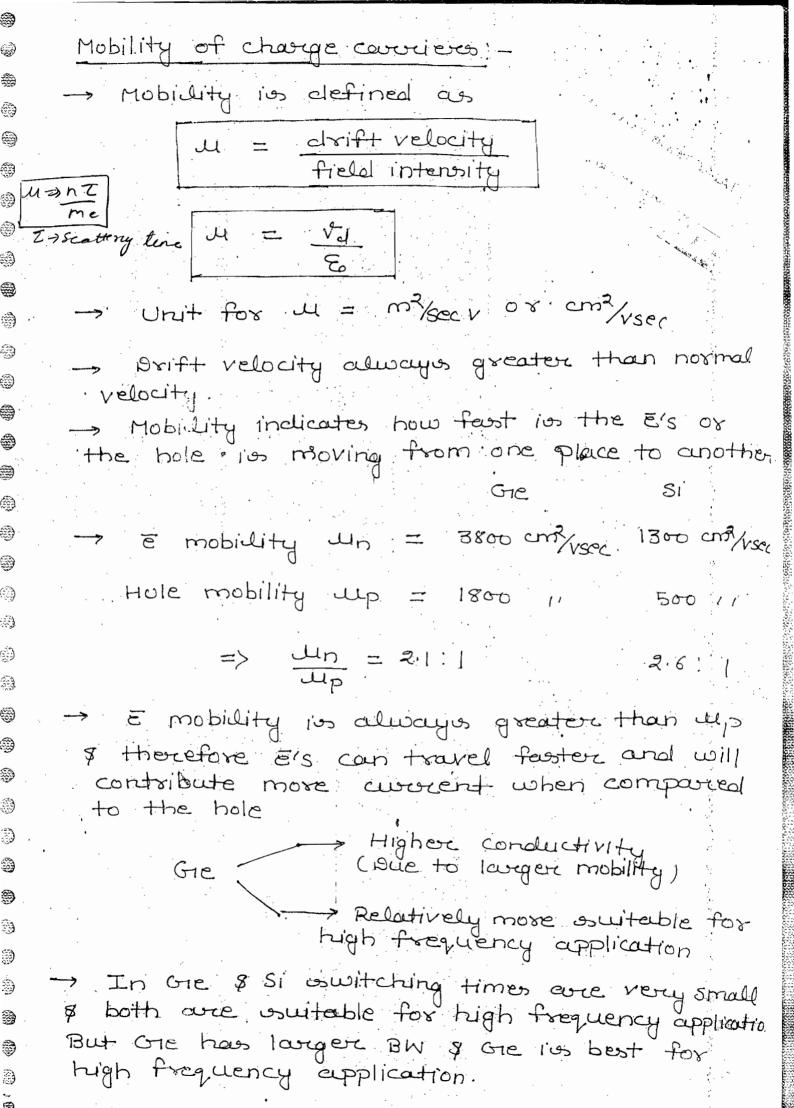

→ Switching time in both one & Si are very small so can work on high frequency but one is better bec. its BW is high.

-> Always mobility dec with temp for all devices. It is a universal statement

-> Mobility of charge coveriers always dec.

-> As temperature inc, the atoms in the material will vibrate and due to thermal vibrations the mobility of charge carriers dec

to Fox Si Fox Gre

m = 2.5 for  $\bar{e}$  m = 1.66 for  $\bar{e}$

= 2.7 for hole = 2.33 for hole

a non-linear variation

#### Cwevent! -

- -> curvient is defined as rate of charge of charge  $i = \frac{dq}{dt}$

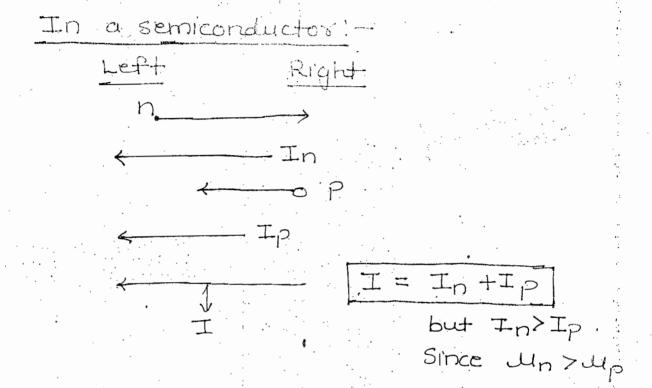

- In a semiconductor, there is a bipolar current i.e. current is coveried by both e's and holes.

#### Briff Cwovent! -

It is the flow of current through the material or device under the influence of field intensity or, applied voltage

voltage -> driving force -> drift current without applying force or voltage -> diffusion current

## operating temperature:

#### (1). For Ge: -.

-60°C to 75°C

-> Max operating temperature is 75°c

#### (11) For Si:

-60°c to 175°c

- -> Max operating temperature in 175°C

- -> si is more esuitable for high temperature application

### Normal Working temperature! -

- working temperature will less than or equal to. 400k; < 400k

- into material oscience

osemiconductor element?

Soln'- In periodic table: - GIP-IV

(1) Energy gap is very large

(11) C has very-2 unstable Si ] Serriconducto

Properties

(III) c having un reliable properties

(IV) C having unpredictable properties

#### NOTE :-

Sometimes, C -> Conductor -> Greaphite

" -> Insulator -> Diamond.

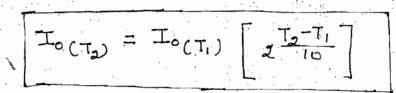

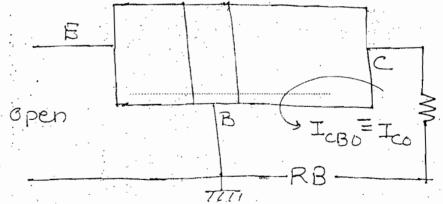

## Leakage Curvient (Io):-

(i)

<u></u>

**)**

٩

(

٨

**(3)**

∰

۹

٩

(i)

4

(;)

- -> Also called minority coveriere currient or thermalle generated current or reverse saturation curve

- Jo depends on minority coveriers and minority of temperature depends on temperature & therefore it is generated because of temperature. Therefore it is thermally generated curverent.

- If leakage current are small, the temper.

-ature effect on material or device will be less

and this indicates better thermal stability

$I_0 = \mu A$  nA (Gie)  $S_i$ )  $I_0$  of Gie  $> I_0$  of  $S_i$

- -> Silicon is having better thermal istability than germanium This is due to ismaller leakage current.

- To is independent of applied voltage ine this current is saturated with applied voltage.

Hence the name saturation current

- In is highly sensitive to temp

- For 1°C, In approximately 1 by 7% in both

- € > To doubles for every 10°C

$$T_{o}(T_{2}) = T_{o}(T_{i} \left[ 2^{\frac{T_{i}-T_{i}}{16}} \right]$$

where T2>T,

| Resistivity (f)                              |

|----------------------------------------------|

| -> specific resintance of the material       |

| -> Unit: - 12 cm or 12 m                     |

| -, For metals!-                              |

| the temperature coeffecient of Resistance    |

| i.e. R1 with 1T                              |

| R=Pl                                         |

|                                              |

| In metale p1 with inc. in temperature        |

| -> For semiconductors!                       |

| -ve temperature coefficient of resinstance   |

| i.e. RI with inc. in temperature             |

| In a sc, P / with 1 in temperature           |

| Conductivity (+):                            |

| > It is the reciprocal of resolutivity       |

|                                              |

| · Unit: - 1 ~ v/cm or v/m                    |

| -> conductivity denotes auscent coverying    |

| capacity of the material or device           |

| Conductivity = converer x charge x mobility. |

| -> conductivity depends on                   |

| (1) carrier conc. (11) charge (111) mobility |

| Variation in conductivity due to temperature |

| depender on:                                 |

| 1) Variation in mobility of charge couriers  |

| 11) Variation in coverier concentration.     |

|                                              |

|                                              |

For Metals: - > uripolar

To = nglin

- In metal of with inc. in temperature

- In metal free & concentration is independ -ent of temperature

- of charge conviers dec. and therefore conductivity decreases.

For semiconductor: - -> Bipolar

3

$(\cdot)$

ᅠ∰ :

٩

ું છે

٩

$^{(+)}$

()

٩

٩

3

( )

= nquin + Pquip

- In a serry conductor, conductivity increases with inc. in temperature

- Tracrease in coverier conc. > dec in mobility with inc. in temperature

- In a semiconductor as temp. inc. mobility of change convieres dec and it will reduce the conductivity slightly and at the same time because of temperature a clarge no. of covalent bond will be broken and large no of it. I hoke are created and this will the conductivity But larger value and the net result conductivity inc. with the temperature

- The a semiconductor conductivity mainly depends on coverier concentration

- -> Semiconductor means by default it is

NOTE !-In intrinsic semiconductor, conductivity increases with inc. in temperature. Curerer Density (J): -> It is the awarent passing per unit area J = IAmp/m<sup>2</sup> J = 0-1811 A/m2 Electric field intensity  $=\frac{v}{m}$ J = mho volt For metals !-

J=nquine A/cm2

For semiconductor! -

J = [ngun + Paup] & A/cm2

conductivity sensitivity! -

- In intrinsic esemiconductor, conductivity increases with inc in temperature

- For 1°C or of Gret by 6%

- -> For 10C of si 1 by 8%

- when compare to Ge, conductivity of Si is more sensitive to temperature. But si is more suitable for high tempt application This is due to small deakage current.

```

Energy Grap! - [Eg] or [Eg] ! -

Egro = Energy Grap at OK

Ecroso = Energy Grap at 300k

· Gre

CB

EG10 = 0.785 eV 1210V

> Forbidden

Energy

EG1300 = 0.72 eV 1/eV

VB

Band

Crap

Energy Band Diagram

of an Element

Energy Grap decreases with increase in the

temperature i.e. | Eg x 1

EGICT) = EGIO-POT EV

Po = Material constant

Bo = eV/OK

For Si! !-

E_{GICT} = 1.21 - 3.6 \times 10^{-4} T

Temp should be in kelvip

For Gie! -

EGICT) = 0.785 - 2.23 × 10-47

```

٩

٠

(ژ

₩.

1

(1)

۹

(3)

٩

(;)

٨

()

٨

3

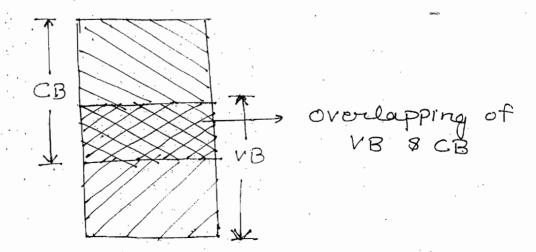

# Energy Band Diagram of Metals/Conductors: -. All metals are very good conductors of curicert i.e. they allow large flow of current through them

- -> All metals are unipolar i.e. current is coverying in metals only by E's

- -> : In metal E conc is very high ie n= 10/m

- -> In metals free e cong is independent of temperature

-> In metals free ers are available even at or

At: 300K:-

-> Overlap 1 with 1 temperature

- · Due to the overlapping of valence band & conduction band, metals having the temperat coefficient of resistance (PTC)

- In metals there will be only drift curven eg! - Gold, Silver, Platinium, Cu, Al etc

# Energy Band Biagram of an insulator:

- -> Insulator are bad conductor of current i.e. they don't allow any flow of current through

- -> Ionie bonding

- -> + = 0 (Ideal insulator)

- = negligible (Practical insulator).

- -> EG = Large

- NTC OF R Negative temperature coefficient i.e. R | with T1 VB

- eg: Diamond, Sioz, AIX, paper, glass etc

For < I

CB compty

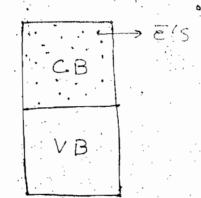

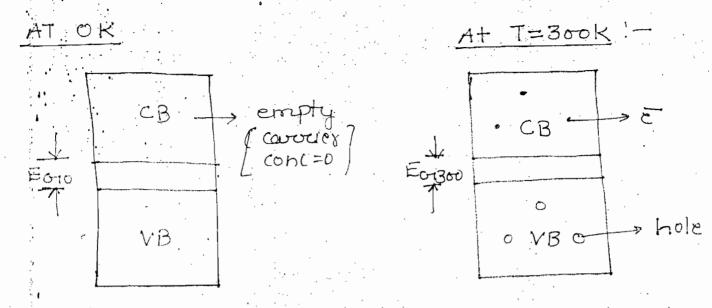

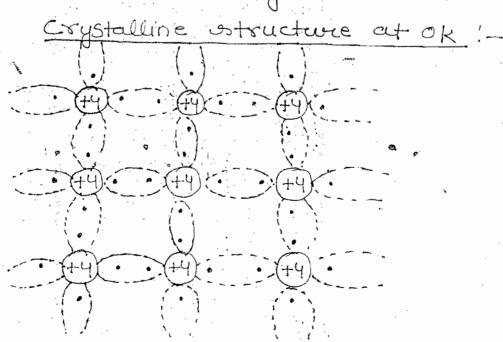

## Energy Bound Diagram of a semiconductor:

- >> Semiconductor belonges to IV the group of perciodic table

- The nature of bonding is covalent bonding Bipolour i'e having two different types of charge carriers.

- For a esemiconductor, the energy gap is small i.e. Eg around lev

0.7ev to 1.5ev

- -> A+ T=0k carriere conc are zero thereby conduction band is empty. Hence conductivity is zero

- -> All serviconductors are insulators at OK

- At room temperature, because of thermal energy a large no of covalent bonds will be broken and equal no of e's and notes are created and there will be a small conduct-ivity in the semiconductor

- Semiconductor possess negative temperature coefficient of resistance

- The a semiconductor there is a diffusion convert

- Definition of Semiconductor:

semiconductor are the elements whose conductivity lies b/w the conductivity of insulator and conductivity of a conductor

#### Einstein's Equation! -

(\*\*)

( )

$(\cdot)$

۹

respect to great oscientist Einstein.

In a semiconductor

$$\frac{\partial n}{\partial u_n} = \frac{\partial p}{\partial u_p} = V_T$$

$$\frac{u_n}{\beta_n} = \frac{u_p}{\beta_p} = \frac{1}{V_7}$$

-> It gives the relationship blu diffusion constant mobility and thermal voltage

-> The unit for mobility to diffusion constant

-> The unit for 12 is volt

## Diffusion constant of charge carriers (D)!

E diffusion constant

$$\beta_n = \mu_n V_T$$

Hole 11  $\beta_p = \mu_p V_T$

Unit for  $\beta !$ —  $Cm^2/sec$

- -> It is a material constant related with the property diffusion

- -> Diffusion constant of the charge coveriers decreases with the temperature

ID = JULY 1 u is more sensitive with temp as compare

$$\frac{1}{2} = \frac{1}{2} = \frac{1}$$

fraction.

NOTE!-

$$\frac{g_n}{g_p} = 2.1$$

## Mass Action Low: -

$$np = n_i^2$$

It estates that, "In a esemiconductor (intrinsic or extrinsic) under thermal equilibrium the product of electrons and holes will be always a constant and is given by sequence of intrinsic concentration.

- The law is mainly used for extrinsic semi--conductor to calculate minority carrier conc.

### For n-type semiconductor !-

Majority caviers are  $\bar{e}$ 's =  $n_n$ Minority // holes =  $P_n$

$$P_n = \frac{n^2}{n_n}$$

## For p-type semiconductor :-

Majority couviers are holes = Pp Minority // E/s = np

$$n_p = n_i^2$$

$p_p$

۹

**)**

۹

( )

$$n_n P_n = n_p P_p = n_i^2$$

The an intrinsic esemiconductor, e's and holes conc. are n & p respectively. By adding impurity atoms; the E & hole conc. are n, & P, respectively then the following relation is acceptable

Before Doping After Doping np = n,2 n, p, = n, 3 $n_p = n_i p_i$ Hence np = n,p, = n,2 Intrinsic Concentration (n;)!-Intrinsic = Purce It is the conc. evailable in the pure semi - conductor at a given temperature  $n = p = n_i$ ni2 = AoT3 e EGYKT where Ao = material constant

$$\dot{n}_{1} = \sqrt{A_{0}} T^{3/2} e^{-E_{G}}/2kT$$

-> Intrinsic concentration in a semiconductor depends on (1) Temperature

Thtrinoic concentration is a solt (b) T3/2

-> Intrinsic concentration n; is & (a) 73

- -> Intrinsic concentration increases with the temperature as a non-linear variation. -> When compare to Si, Gre is having larger value of n; and it is due to smaller value of energy gap A+ 300K!-For Gie -> n; = 2.5 x 1013 atoms/cm3 For Si -> n; = 1.5 x 1010 extorms /cm3 Electrical Properties of Germanium & Silicon! Properties Atomic No. Total No of atoms / cm3 4.421 X 1022 5 × 1022 Density of atoms Intrinsic conc. ni at 1.5×1010 2.5 × 10<sup>13</sup> 300k (atoms/cm3) Intrinsic resinstivity P at 9. 230,000. 45 300K (2) cm 9 5. Leakage current (Io) UA. nAMax operating Temperature 75°C 175°C 9 T Power handling Capability low high

- 3 8. E 010 q. EGI300 9 10 Mn

- 9 11 Up.

(3)

٩

(ق

۹

(1)

- 12 Dn.

- P P 13

Si + 02 -> SiO2

Cheapent insulating material

- -> Silicon is more fancy when compare to Greduce to

- (1) Smaller leakage curvent

- (11) High temperature application

- (111). Suitable for low power & high power. handling

- (IV) Plenty available on the swiface of earth

- by inemiconductor device manufacturer

- (V) Cheapent Material

- (VI) Favourable properties to form SiO2

main

This is the noceason why Si is fancy

by IC manufactureers

#### NOTE !-

- 1. Si when exposed to 1400°c we get liquid si which reacted with 02 to give 5102

- 2. Sion is used to provide isolation in between the components inside the IC

## Bisadvantage of Si:

The main disadvantage of Si is smaller conductivity

#### Diffusion & Diffusion current!

- -> Biffusion is a natural phenomenon.

- The migration of charge coverients from higher conc. to lower conc. or from higher density to lower density is called diffusion.

- -> Diffusion is mainly due to conc. gradient

dn -> 5 lope -> Gradient

dn -> e conc. gradient

$\frac{dP}{dP} \rightarrow \text{hole } "$

#### Sinconductor

Higher Lower Conc.

- Diffusion current flows only in semiconductors.

- Jn a esemiconductor, diffusion is due to unequal distribution of charge coveriers

#### NOTE :-

(1)

٩

9

In metal, E conc. is very high (n=1028/m) and therefore E are arranged with equal.

distribution Hence diffusion cannot takes place

Tiffusion is also associated with random

motion of charge the coveriers due to thermal

Vibrations.

# enath of Diffusion! L = VB.7 cm D > diffusion constant of charge C -> coverer lifetime / Average lifetime Length of diffusion is average length Since D = UVT · L = VULVT Cm Length of diffusion depends on (1) Diffusion constant of charge coverers (11) Mobility of charge carrier. (111) carrier life-time (IV) Temperature. Electron diffusion length, In = VAnta cm MHole diffusion length, Lp = VapTp cm E diffusion current density, Tunction $J_n = +9 \beta_n \frac{dn}{dx} A/cm^2$ (Biff) Hole diffusion current density, Jp (Aiff) = -9, Ap dP A/cm? Electron diffusion current :-

In (Aiff) = In (Aiff) x Area

Hole diffusion avocent Ip (Diff.) = Ip (Diff.) X Area Note! -By default always consider unit cross sectional area Total current density in a isemiconductor! The total convert density in a semiconductor J = Jn + Jp A/cm? Jn = Jn (AITT) + Jn (ARIFT) Jn = 9 Pndn + nqunE A/cm Jp = Jp (Drift) + Jp (Diff.) Jp = Pq. Up& - q. Apdp A/cm2 O NOTE: Drift concent depends on (1) conviere conc. (11) Charge (III) Mobility of charge coveriers CIV) Field intensity Drift aucent mountydepends on field intensity Diffusion awarent mainly depends on concentr. -ation gradient > In a semiconductor total diffusion current density is given by J (Diff.) = Jn (Drift) + Jp (Diff.) to andn - o ap dp

Quest- If drift velocity of holes under the field gradient of 100 V/m Find its mobility

Ansi- &= 100 V/m

Va = 5m/sec

= 5 = 0.05 m<sup>2</sup>/vsec / Ansi

Quest The coveriese mobility in a semiconductor

Ans: - U = 0.4 m<sup>2</sup>/vsec

$\beta = ?$ At T = 300k  $V_T = 26 mV$

$D = UV_{7}$ = 0.4 (26 × 10<sup>-3</sup>.

= 0.0104 m2/sec , Ans.

the diffusion constant in a semiconductor are looused and looking sec respectively.

Find the diffusion length of charge coverier

Ans: - F = 100 UISec

B = 100 cm²/sec.

L = √25

= V100 x 100 x 10-6

= 0.1 cm, Ans

aues: - A osample of n-type semiconductor has E density of 6.25 × 1018/cm3 at 300K. If the intrinsic conc of charge carrière in the sample is 25 x1013 cm3. Find the hole conc. Ans: N-type SC  $n = 6.25 \times 10^{18} / \text{cm}^3$  $h_i = 2.5 \times 10^{13} / \text{cm}^3$ By Mass action Law  $P = \frac{n^2}{n} = \frac{(2.5 \times 10^{13})^2}{6.25 \times 10^{18}} = \frac{10^{18}}{cm^3}$ ·Quesi- A flat Al ostrip with a resistivity of 3.44 X 10-8 sz m and a length of 5mm with a cross-sectional larger is 2x10 mm? is osubjected to a current flow of 50 m A Fird Voltage drop across it Ans: - P = 3.44 x 10-8-12 1 = 5mm a = 2 x 10 4 mm? I = 50mA  $R = P = 0.86 \Omega$ V = IR = 43 mV, Ans

(

۹

439

٩

(3)

8

۹

(3)

٠

۹

(9)

(9)

9

aues! - A semiconductor Wafer is 0.5 mm Hick A potential of loops is applied across the thickness

(1) What is the & drift velocity ?if the mobility is 02 m2/vser

(11) How much time is required for an e to mon

Ans - (1)

$$2c = 0.5 \text{ mm}$$

$$= 0.05 \text{ cm} = 0.5 \times 10^{-3} \text{ m}$$

$$V = 100 \text{ MeV}, = 10^{-4} \text{ V}$$

$$E = 10^{-4} \times 10^{-2} = 0.2 \text{ Voit/m}$$

$$0.5 \times 10^{-3}$$

$$V_d = UE$$

$$= 0.2 \times 0.2 = 0.04 \text{ m/sec}.$$

(11)  $t = \frac{\infty}{\sqrt{2}}$

$$= 0.5 \times 10^{-3} \times 10^{2} = \frac{5}{4} \times 10^{-2}$$

$$= 0.5 \times 10^{-3} \times 10^{2} = \frac{5}{4} \times 10^{-2}$$

$$= 0.5 \times 10^{-2} \text{ isce}.$$

(aues: A small conc. of minority conviews are injected into a homogeneous, semiconductor crystal at one point and having electric field of 10 V/m is applied across the crystal shows of 10 V/m is applied across the crystal will be moving a distance of 1cm in 20 usec calculate the mobility in cm/sec.

Solp - . E= 10 V/cm = 10 of V/cm

£ = 20 USEC = 20 × 10-6 SEC.

x = 1cm

$v_{d} = \frac{x}{t} = \frac{1}{20 \times 10^{-6}} = 50,000 \text{ cm/sec}$

$M = \frac{V_d}{c} = \frac{50,000}{5000} = \frac{5000 \text{ cm}^2/\text{vsec}}{10000}$

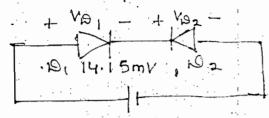

cours! - In Gie, leakage convert are 5 MA at 10°C: Find its value when the temperature is 25° C.

$$T_{0}(T_{1}) = 5 \text{ MA}$$

$T_{1} = 10^{\circ} \text{C} = 283 \text{K}$

$T_{0}(T_{2}) = 7$   $T_{2} = 25^{\circ} \text{C} = 298 \text{K}$

$T_{0}(T_{2}) = T_{01} \left[ 2^{(T_{2}-T_{1}/10)} \right]$

$T_{02} = 5 \left[ 2^{25-10/10} \right] = 14.14 \text{ MA, Am}$

#### NOTE !-

(1)

Semiconductor is non-linear element Hence we can't applied ohm's Law

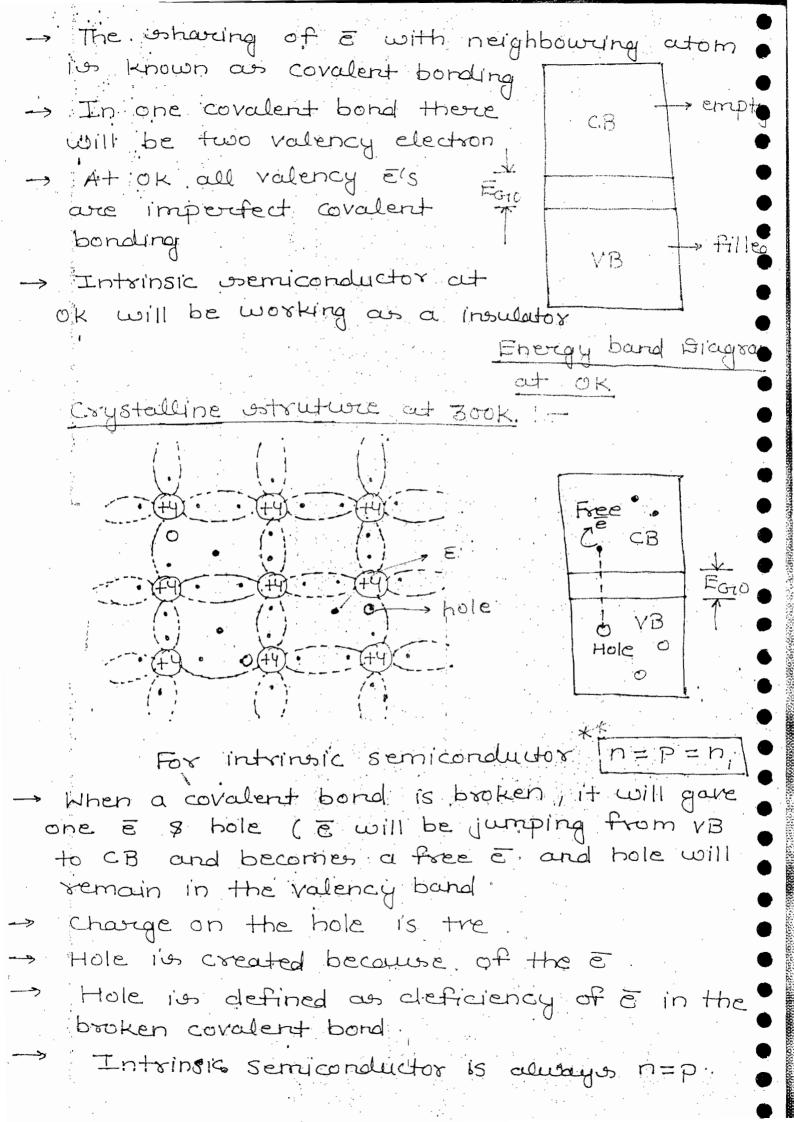

## Intrinsic Semiconductor!

- -> also known as pure semiconductor or national semiconductor or non-degenerate semiconducto:

- The outermost orbit in an atom is known as (3) valency band.

- -> The max no of valency E's are 8.

- -> The condition for intrinsic esemiconductor n=p=n;

- -> Because of opposite charges electron & hole always move in the opposite direction.

٠

۹

8

٠

۹

٨

( )

- -> convert direction is opposite to the flow of E's

- -> convert direction is in the direction of

- To a semiconductor, & and holes always moves in opposite direction but they contribute the current in the same direction

- The free e's will be moving in the conduction band and will contribute same current and at the same time hole will be moving in the Valence band and will contribute the same current and the total current is electron current those current.

(1) Conductivity of intrinsic semiconductor! -

$$\sigma_i = n_i u_n + p_i u_p$$

but  $n = p = n_i$

$\sigma_i = n_i v_i u_n + u_p_i$

but n; 2 T3/2

Hence To with 1 in Tous a non-linear

(II) Intrinsic Resistivity!

$$f_{i} = 1$$

$$P_{i} = 1$$

$$n_{i} \circ [u_{i} + u_{p}]$$

Disciplification of intrinsic semiconductor! -

The major disadvantage is smaller conductivity

NOTE! The vonly electronic device fabricated with intrinsic semiconductor is PIN diode

.111) Greneration of E hole pairs!

of E's and holes are created This process is called as generation of E hole pair.

#### (IV) Recombination:

is known as recombination.

- -> Awing recombination, free \( \varepsilon \) and hole both will disappear and a covalent bond is created

- -> During the recombination, the free & will be falling from conduction band to valency band to recombine with the hole.

#### (V) Covier lifetime (T)!-

- of covalent bond until its recombination

- -> 7 is average lifetime.

- -> I is in the range of usec to nsec.

#### NOTE:

- -> Hole is basically a valency electron for assumed with a tre charge

- -> Hole is considered with a tre mass

.

Lecture - 4 - The process of adding the implusities to the semiconductor is called doping. Joping increases the coverier concentration and hereby increases the conductivity Trivalent / Acceptor impurities: By Ad, Gra & In Pentewalent / Donor impurities: - P, As, Sb & B1 impurity atom. More affinity Doping is based on 1:106 or 1 in 10 or 1 Standard Doping Concentration: (1) Moderate Doping -> 1: [106 to 108] -> P N

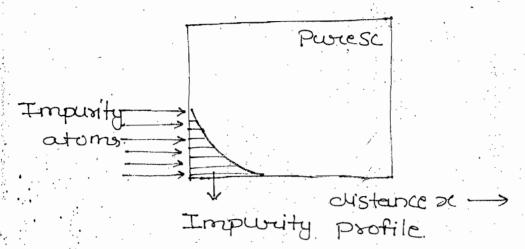

(11) Lightly Doped -> 1: 1011 -> P N (III) Highly/Heavely doped -> 1:103 -> The minimum doping required to convert intrinsic semiconductor to extrinsic esemiconductor is 1:108 -> When intrinsic osemiconductor is lightly doped it will remain intrinsic -> \*\* With 1:10 doping in Gie, - 1 by 12 times > \* with 1:10+ // 11 11 / ~ // (cupprox 120 Hm -> In a natural osemiconductor / intrinsic semiconduy Decourse of unequal distribution of charge coverer there will be always a & diffusion current \* - Even when a voltage is applied there will be no drift auscent The impurities atom or doping or impurities profile can be homogeneous or non-homogeneous > The impurities profile must be introduced, built in electric field or internal electric field in the esemiconductor uso that esemiconductor

will not be having a drift awarent along with

It will remain intrinsic But due to the impurity profile there will be drift current along with a diffusion avocent.

The impurity profile will be maximum on the swiface of a isemiconductor where it is introduced and the profile gradually decreases as a exponentially decaying function with the distance into the semiconductor.

#### NOTE! -

-> Trivalent and pentavalent impurities when added to the overniconductor will introduce built in electric field.

# Ore-Sicrystal :-

- to the Gre as impurities, we get Gre-Si Crystal.

- -> The nature of the bonding is covalent bonding

- -> At OK there will be working as a insulator.

- -> At 300k they will be working as intrinsis

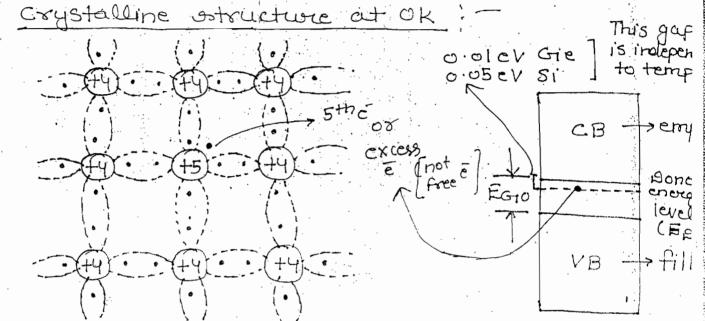

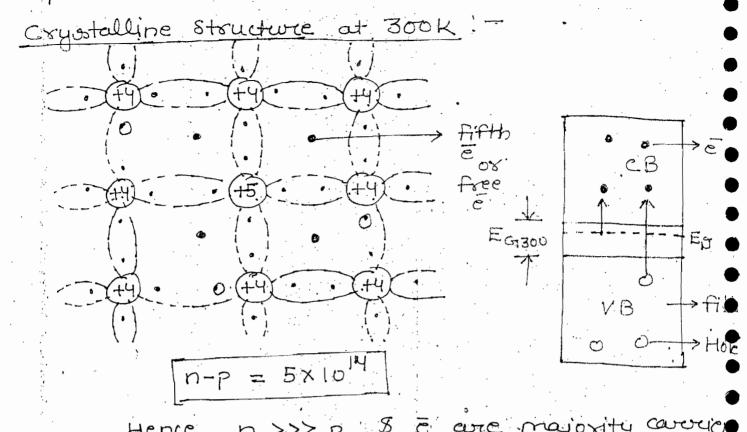

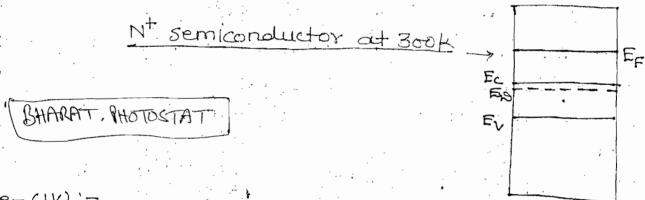

# Extrinsic Semiconductor/Boped Semiconductor:

or degenerate SC or compensated SC.

Types of Extrinsic Semiconductor: -

- (1) N- type semiconductor or BONAR: -

- -> The impurity is pentavalent

#### NOTE !-

- -> BONAR energy level is a discrete energy level.

- of pentavalent atoms added to the semicanduce

- will be existing in the donor energy level.

- The additional energy required to detach the fifth E from it's orbit = o olar for Gie.

- -> n-type eservicenductor at ok will be working as a insulator

- No. of 5th  $\bar{c} = \frac{51}{5 \times 10^{22}} \frac{\text{atoms } \times 10^{8}}{\text{cm}^3} \times \frac{1}{10^8}$

- = 5×1014 atoms/cm3

8 holes are minosity coveriers

- The n-type osemiconductor , every impurity atom will be donating one & into the conduction band and therefore it is also called as a donar.

- -> Bonave level ionisation indicates the fifth e's moving from donave energy level into the conduction band

- temperature (i.e. as tempt is increasing from OK to 300K, the fifth & will be moving from donar energy level to conduction band)

- is completed ( i.e. the fifth & of all the impurity atoms as shifted from donar energy level into the conduction band)

- -> Above 300K there is no donar level ionization

- The fifth E will be moving from donar to

energy level to conduction band and at the same time because of thermal energy a large no of covalent bond are broken and equal no of e's a holes are created and all these e's will be moving from valence band to conduction band. The e concentration in the conduction band is more greater than the hole concentration in the valence band. The e are majority and holes are minority cavagers.

(3)

$\odot$

়ি

-> Majority carocious will contribute more current with leas noise

-> Minority carriers will contribute less current and more noise.

-> Minority convoice noise is thermal noise/white noise / Johnson noise. It increases with the temperature.

minority carriers will vibrate and due to thermal vibration they produce more noise.

-> The condition for n-type esemiconductor is

n > n; P < n;

The n-type semiconductor, as a conc. increase above n;, the hole conc will be falling below n; and this is due to a large no of recombination

-> According to law of electrical neutrality

$N_{0}+P=N_{A}+n$

In n-type semiconductor

$N_A = 0$   $N_B + P$

where

No = Bonox conc

ox

density of

density of donox atom

$n \approx N_{\theta}$

- added to the semiconductor

- In n-type semiconductor, curvent is predone inated dominated by electrons.

- In n-type semiconductors, the free & conc.

1's approximately = density of donor atoms

- (i.e. approximately equal to NA)

- is almost negligible.

- -> The conductivity of n-type semiconductors is

- -> Representation of n-type semiconductor is

- In n-type semiconductor, after donating the & will be gaining the tre charge and will of become tre ion

# P-type semiconductor or Acceptor! -The impurity is trivalent Cryotalline ostructure at OK ordleV C 0.05 CVIS CB Borro Ecro r. Acceptor energy level -> Acceptor energy level is a discrete energy level created just above the valency band. -> Acceptor energy level denotes energy level of all the trivalent atoms added to the pur serviconductor > p-type semiconductor at OK will be works as a insulator. Cryotalline estructure at 300K: AB O Hule

3

()

9

3

In p-type semiconductor, every impurity atom will be receiving one è to complete its covaler bond Hence it is acceptor → Since P>>n In p-type semiconductor at room tempt, because of thermal energy a large no of. covalent bonds will be broken and equal no of E's & holes are created and most of these E will be moving from valency band to acceptor energy level to complete the bording and a very few e will be moving from valency band to conduction band and therefore holes are majority carriers. The hole conc. in valency band is far greater than hole conc. in conduction band Hence holes are majority carrier and ē are minority coveres. In p-type, semiconductor, current is dominate by holes. > Positre type semiconductor (>> P-type > The condition for p-type semiconductor is  $P > n_i$   $n < n_i$ In p-type semiconductor as hole cone is increasing above in, the hole cone will fall below ni This is due to large no of bording According to law of electrical neutrality: No +P=NA+n In p-type semiconductor  $N_{P}=0$   $P=N_{A}+n$  and  $P\approx N_{A}$

The conductivity of p-type esemiconductor is p = nquln + pquip v/cm p = pquip v/cm p = pquip v/cm

Representation of p-type esemiconductor!

Low of Electrical Neutrality:

$\rightarrow$  It is based on law of conservation of charge  $\rightarrow$  i.e. total tre charges = total -re charges  $\frac{1}{2}$   $\frac{1}{2}$

NA = Acceptor conc. 8 is associated with the NA = Acceptor conc. 8 is associated with -ve charge!

$$\Rightarrow$$

$N_B - N_A = n-P$

-> Any semiconductor accepting how of electrical neutrality will be always electrical neutrality

-> For intrinsic esemiconductor 1-

$$N_A = 0$$

$$P=n$$

$P-n=0$

It is electrically neutral.

-> For n-type esemiconductor!-

$$N_A = 0$$

For p-type isemiconductor! -.

$$P = N_A + n$$

$$P \simeq N_A$$

-> All semiconductors are electrically neutral

Cures N-Type semicorductor is.

- (a) vely charged (b) trely charged

- (c) No charge estable jet) electrically neutral

### Lecture -5

intrinsic as well as p-type & n-type.

Ques: - calculate intrinsic conductivity and intrinsic ocessistivity of Gre at 300k. Assume n; = 2.5 x 10/3 atom;

Un = 3800 cm²/vsec Up = 1800 cm²/vsec

Soln:- = n; 2 [ wn + wp]

= 2.5 × 10<sup>13</sup> × 1.6 × 10<sup>-19</sup> [ 3800 + 1800]

= 0.0224 25/cm

$= \frac{1}{0.0224} = 44.6 \Omega cm$

purce Si at room temperature n; = 1.5 × 1010 atoms/ un = 1300 cm²/vsec Up = 500 extm²/vsec

\$5010:- 0; = n; q [un + up]

=  $1.5 \times 10^{10} \times 1.6 \times 10^{-19}$  [1300 + 500]

= 4.32 × 10-6-5/cm

$f_{i} = \frac{1}{4.32 \times 10^{-6}} = 231481 \Omega cm$

donox impurities to the extent of I impurity atom

for every 107 atom, calculate

(1) Bonor conc.

(11) Electron & hole conc.

(111) conductivity & resinstivity of doped servicoirductor

(IV) How many times conductivity is increased in the osemiconductor due to doping? Assume total pp of atoms = 4.421x10./cm3 n; = 2.5 × 1013 atoms/cm3 un = 3800 un3/vsec ULP = 1800 11 Soln: (1) No = total no of atomo/cm3 x Impurity ratio 4421 × 1022 × 107 = 4.421 × 1015 atoms/cm3 In n-type semiconductor (11)n ~ No = 4.421 x 1015/cm3  $P_0 = \frac{n_1^2}{n} = \frac{(2.5 \times 10^{13})^2}{4.421 \times 10^{15}}$ P = 1.41 × 1011/cm3 TN = Na ? Un (111) = 4.421 x 1015 x 1.6 x 10-19 x 3800 = 2.68 T/cm  $f_{N} = 1 = 0.373 \Omega cm$ (IV) Before doping the osemiconductor is intrinsic. = n; 9 [ Un + Up] = 2.5 x 10<sup>13</sup> x 1.6 x 10<sup>-19</sup> [3800 + 1800] = 0.0 224 To /cm By adding donor impurities 1: 107 the conductivity of semiconductor is increased from 0.0224 to/cm to 2.68 J/cm. Increased conductivity due to doping 1 = 2.68 = 119 = 120 times 0.0224

ours: - A pure esemiconductor is doped with acceptor impurities to extent of 4 impurity atom for every imillion of atoms (106) calculate its conductivity Soln:-Acceptor impurition = 4:106 Total no of atoms = 5 x 1022/cm3 n; = 1.5 × 1010 atoms/cm3 Un = 1300 cm2 V/sec up = 500 " NA = 5 x 1022 x 4 = 2 x 1017 atom/cm3 op = NA 2 Mp 2 x 1017 x 1.6 x 10-19 x 500 ~ 16 V/cm Quest- A purce semiconductor (Si) is doped with donor impusities to a extent 1:106. Calculate (1) Conductivity due to majority coveriors (11) " in minority Assume total no of atoms = 5 × 1022/cm3 n; = 1.5 × 1010 atoms/cm2. Un = 1300 cm² /Vsec dip = 500 11 11 Soln! -In N-type semiconductor

٩

٩

٩

(3)

٩

٠

۹

٧

۹

(ĕ)

(زِرُّ)

(3)

3

(E)

۹

**(3)**

٩

3

$= 5 \times 10^{16} \times 1.6 \times 10^{-19} \times 1300 = 10.4 \text{ T/cm}$

P = No Un o

(1) canductivity due to majority coveriers:

$$N_{B} = \frac{1000}{100} = \frac{1000}{100} \times 1.R$$

$$= \frac{5 \times 10^{22} \times 1}{100} = \frac{5 \times 10^{16}}{100}$$

$$= \frac{n_{1}^{2}}{N_{B}} = \frac{n_{1}^{2}}{N_{B}} = \frac{1000}{100} \times 1.6 \times 10^{-19} \times 500$$

$$= \frac{(1.5 \times 10^{10})^{2}}{5 \times 10^{16}} \times 1.6 \times 10^{-19} \times 500$$

Quest In a semiconductor at room temperatural the intrinsic conc. & intrinsic scesistivity are 1.5 × 10<sup>16</sup> / cm<sup>3</sup> & 2 × 10<sup>3</sup> Ω m respectively. It is converted into extrinsic semiconductor with a cloping concentration of 10<sup>20</sup>/cm<sup>3</sup> for the extrinsic semiconductor calculate

(1) Minority coverier concentration

(111) Resisstivity

(111) Electron mobility

(IV) Minority carrier conc. when its temperature is increased to a value at which the intrinsic carrier conc. is doubled.

Assume up the mobility of majority coveriers is equal to the mobility of minority coveriers.

Soln:

$$=\frac{1}{2\times10^3}$$

$=\frac{1}{2\times10^3}$

Minority coverier conc =  $\frac{n_i^2}{\text{Poping conc}}$   $= \frac{(1.5 \times 10^{16})^2}{10^{20}}$

= 2.25 × 10 13/m3

V7 = 26 mV Un = 1350 cm? / Vsec.

્ં)

(3)

**(3)**

8

(ž)

**(3)**

( )

\*

(3)

()

(1) The magnitude of electric field at x = 0.5 mum Na= 1016/m3 ca) 1-kV/cm (b) 5kV/cm Set lokV/cm (d) 26 KV/cm density (11) The magnitude of E drift at of = 0.5 um 15 (a) 4.32 X 103 A/cm2 (b) 6.48 x 102 A/cm2 (ce) 2.16 × 104 A/cm2 (d) 1.08 × 104 A/cm? Soln: - (1) | & | x=0.5um = ?  $|\xi|_{x=0.5 \text{ mm}} = \frac{|V_{x=0.65 \text{ mm}}|}{x=0.5 \text{ m}} = \frac{0.5}{0.5 \times 10^{-6} \text{ m}}$ 181 = 10° V/m = 104 V/cm = 10 kV/cm (11) 1 Jn (Arift) = ng, un 18/20=0.5 um n = Na = 1016/cm3  $= 10^{16} \times 1.6 \times 10^{-19} \times 1350 \times 10^{4}$ = · 2.16 × 104 A/cm<sup>2</sup> Minimum conductivity in the semiconductor: -The conductivity of a semiconductor is = = nquin + Pquip -C1) > By mass action law  $P = \frac{n^2}{n} - (11)$ substitute eq-(11) in eq-(1), we get = nquin + ni2quip Differentiate above egn with n do = quin + (-1, p) n, 2quip

=>

$$\frac{d^2 - d^2}{dn^2} = 0 + (+\frac{q}{n^2}) n_i^2 q_i u_p$$

Since second derivative is the , we get condition of minimum conductivity in a semiconductor

The title equation of min conductivity can be obtained by  $d\sigma = 0$

=>

$$0 = \sqrt{4n} - \frac{n_1^2}{n^2} \sqrt{4n}$$

=>  $u_n = \frac{n_1^2}{n^2} u_p$  =>  $n^2 = n_1^2 \frac{u_p}{u_n}$

=>  $n = n_1 \sqrt{4p}$  — (A)

- (3)

$(\cdot)$

( )

٨

(3)

3

The above equation indicates the conc. of E's in the esemiconductor when conductivity is minimum

Substitute eq.(A) in eq.-(11)

$$P = \frac{n_i^2}{n_i \sqrt{\mu p}} \Rightarrow P = n_i \sqrt{\frac{\mu n_i}{\mu p}}$$

Equation -B denotes conc. of hole in the semiconductor when conductivity is minimum substitute eq-(A) & (B) in eq-(1), we get

the equation for minimum conductivity

$$= n_i \sqrt{\underline{u}_n} q_{un} + n_i \sqrt{\underline{u}_n} q_{up}$$

aus: A esemiconductor has the following parame - eters un = 7500 cm²/vsec Up = 300 11  $n_1 = 3.6 \times 10^{12} / cm^3$ Find (a) min. (b) Hole conc. in the semiconductor when Tis min. conc in the semiconductor when is minimum. Soln: - (1) min = 29 n; Vunup = 1.7 × 10-3 ~/cm (11)  $P = n_i \sqrt{un/up} = 1.8 \times 10^{13} / cm^3$ . (111) n = n; \up/un = 7.2 x 1011/cm3 Ques: The diffusion constant for hole in Si is 13 cm²/sec. What is the diffusion current if the gradient of hole conc. is -2 x 1014 holo/cm3 (a) -0.416 mA (b)  $-3.2 \times 10^{-5} \text{A}$  cc) +32 u.A(set) + 0.416mA Soln Ip(piff.) = Jp(piff.) x Area = - V Dp dP x Area By default, Area = 1 cm? IP (A) FP.) = -1.6 × 10-19 (13) [-2×1014]x1.

= + 0.416 mA, Ans

•

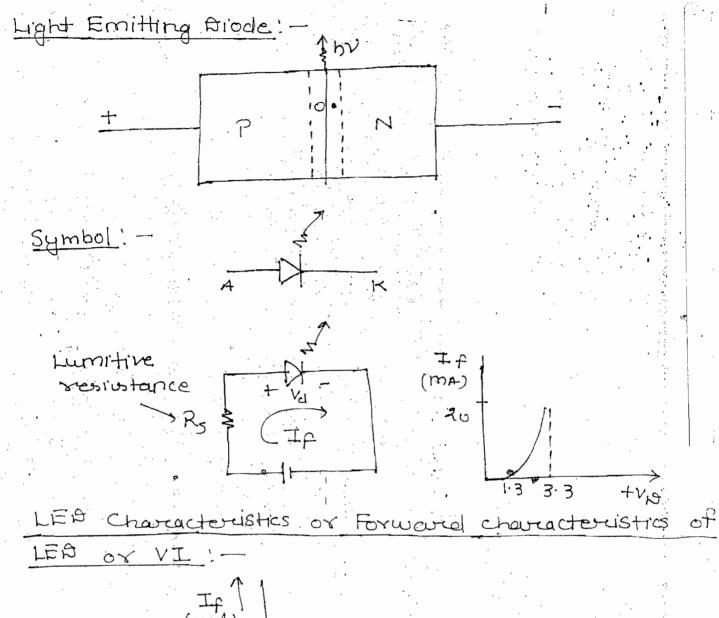

# Gallium - Arsenide (Gras):-

- 9 TH is a compound obtained with Gra from 3rd group & As from 5th group

- It is the best example of direct burdgap semiconductor material.

- energy released in the form of light.

- Grans emits Infrared radiation

- -> Ceilling Noltage = 11.31

- -> EGO = 1.43 eV

٩

- -> Un = 5600 cm²/vsec + 8500 cm²/vsec Up = 400 cm²/vsec

- -> Higher conductivity

- -> Sitting times are very ismall:

- -> Suitable for microwave switching application

- fastest esemiconductor material.

- Low noise microwave material

- proise i'es very esmall

- Grads is used in the fabrication of lover, LED, PIN diode, IMPATT diode, Tunnel diode, Varactor diode and microwave Ic's

- An alternative for GaAs is Inp

- of Grads exhibits -ve differential mobility & due to this property it is more suitable for higher frequency or microwave application

- The nature of bonding in GaAs is mixed bording. For objective type -> it is covalent bonding.

- or p-type GaAs by adding amphoferic material

- when Gie, Be, Zn, Cd are added to gallium arosenide they will be working as acceptor in Gials and they was replace the Gia so we get P-type Gials

- will be working as donors in Gras and replace the As. we and we get n-type Gras

- -> When Si is added to Grass, we get n-type Grass.

# Carrier Concentration: -

They are charge carriers which are contributions

Correier Conc. in intrinsic semiconductor:

In intrinsic esemiconductor covorier conc. means E 8 hole conc

Effect of temperature on carrier conc. in intrinsic semiconductor:

$n=p=n_1$ But  $n_1 \propto T^{3/2}$

Hence n1 withT1 & P1 with T1

In intrinsic esemiconductor carrier concinereases with the temperature.

Effect of temperature on the conductivity of intrinsic isemiconductor!

$T_i = n_i \cdot \left[ \text{Luntup} \right]$   $T_i \cdot \left[ \text{An}_i \right]$ but  $n_i \cdot \left[ \text{AT}^{3/2} \right]$   $T_i \cdot \left[ \text{With T} \right]$

In intrinsic esemiconductor, conductivity increases with the temperature.

Effect of temperature on the mobility of charge carriers:

Mar-m

٩

**3**

$\widehat{(}$

۹

(

3

(1)

Mobility of charge carriers is always dec with the temperature.

coverier conc. in extrinsic osemiconductor:

In extrinsic isemiconductor, conductives mainly due to majority carriers and therefore in extrinsic SC carrier concorneans majority carrier concorneans

Effect of doping on coverier conc. -

N-type SC

Majority carociors are E's Majority carociors are holes:

P=NA

P=NA

doping.

Effect of doping on majority & minority coveres:

Majority coveres are  $\overline{\epsilon}$ 's  $n \approx N_{P}$ Minority coveres are holes  $p = \frac{n_{1}^{2}}{n} = \frac{n_{1}^{2}}{N_{P}}$ For P-Type SC

Majority covoriers are holes P=NA

Minority carriers are E'S  $n = \frac{n_i^2}{P} = \frac{n_i^2}{N_A}$

Majority coverier conc. & Doping

Minority coverier conc. & 1

Doping Conc.

Doping inc. majority coveriers and simultancounty dec minority coveriers.

Effect of doping on the conductivity of extrinoic exmiconductor:

For N-type SC

Un ben = Na

GN & NB

For P-type sc TP = NAquip In extrinsic esemiconductor, conductivity inc. with the doping.

- -> A highly dopens semiconductor exhibits metallic properties i.e.

- (1) Very larger conductivity

- (11) NTC of resistance in the semicorductor will become PTC of resistance.

- (III) Bipolar nature of semiconductor will worked

- -> A highly doped semiconductor will work as a conductor.

Effect of doping on the mobility of charge courses:

As doping increases, the conc. of atoms in the semiconductor inc. and thereby mobility of charge carriers decreases.

Mobility of charge carriers will always decreases with doping.

#### NOTE! -

۹

$\bigcirc$

In the absence of any derived equation for mobility we always consider mobility of charge carriers will remain same before and after the doping for solving the proble Effect of temperature on majority & minoric carriers:

considering a bar of si material when it is pure, n=p=n;

= 1.5 x to 10 atoms/cm3

By adding pertervalent impurities of 1:106, semiconductor becomes n-type  $Np = 5 \times 10^{22} \times 1 = 5 \times 10^{16} \text{ atoms/cm}^3$

In N-type semiconductor at 300K Majority carriers are  $\bar{e}$ 's  $n \approx N_B \Rightarrow 5 \times 10^{16}/\text{cm}^3$  Minority carriers are holes  $P = n_1^2 = (1.5 \times 10^{10})^2$

$P = \frac{n!^2}{n} = \frac{(1.5 \times 10^{10})^7}{5 \times 10^{16}}$

P = 4500/cm3

Let Temp ↑ i.e. T>300K

Let 106 covalent bonds are broken

Thermally generated E's => 106/cm3, holes => 106/cm3

10° E's will be moving from VB to GB

Total no of  $\overline{e}$ 's in the CB  $n = 5 \times 10^{16} / \text{cm}^3 + 10^6 / \text{cm}^3$  (n = Np + P)

n = 5 x 1016/cm3

1 in majority cavorier conc. due to tempt is negligible

Total no. of holes in the VB  $P = 4500/\text{cm}^3 + 16^6/\text{cm}^3$   $\Rightarrow P = 10^6/\text{cm}^3$

1 in minority coverier conc. is almost independent of temperature

Minority coverier conc. will be increasing with

the temperature.

APPEC C

#### Lecture -6

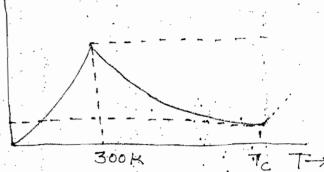

Effect of temperature on the conductivity of extrinsic semiconductor:

for extrinsic semiconductor

-> At OK carrier conc. Is zero Hence, conductivity is zero

- -> Semiconductor curves are always non-linear OK-

- -> Below room temperature in extrinsic isemiconductor the conductivity increases and at room temperature conductivity is maximum and after room temperature

- the conductivity decreases with temperature ( due to mobility )

- -> At civile temperature (Tc) minority caviller conc = majority caviller conc. then the extrinsic semi--conductor became intrinsic

- is minimum and min is slightly greater than to

#### AT TOK!

٠

٩

(%)

(3)

₩.

(3)

(\*\*;)

(3)

۹

٩

(:)

$(\cdot)$

٩

۹

carrier conc are zero and therefore conductivities zero and extrinsic semiconductor at ok will be working as an insulator.

# At OKKTK300K:-

As temperature is increases because of thermal energy, a large no of covalent bonds will be broken and equal no of electrons and holes are created and due to the doping majority and minority carriers are created and the conductivity of the extrinsic semiconductor will be increases with the temperature.

### AT T= 300K! -

The conductivity of extrinsic semiconductor is maximum.

# At BOOK KTK To !-

- -> Majority carrier conc will remain almost independ-

- -> Minority carreier conc. will be increases with the

- -> The temperature is increases, mobility of charge carriers decreases and therefore the conductivity of extrinsic semiconductor will be decreases with the temperature

# A+ T=Tc!-

At curier temperature minority avoier conc approaches majority coverier conc. and extrinsic semiconductor will become intrinsic semi- conductor and conductivity will become minimum.

#### 町った!一

Above the curic temperature, since the semiconductor is intrinsic, its conductivity will be increases with the temperature.

- Conductor will work as intrinsic esemiconductor

- (1) At very high temperature extrinsic semiconductor will become intrinsic esemiconductor

- (11) At low temperature, the conductivity of extrinsic semiconductor will be increases with the temperature.

- (III) In extrinsic semiconductor as temperature increases, its conductivity decreases

(consider above 300K)

٠

٠

4

٨

٩

(3)

٨

$\langle \cdot \rangle$

(3)

4

٩

٧

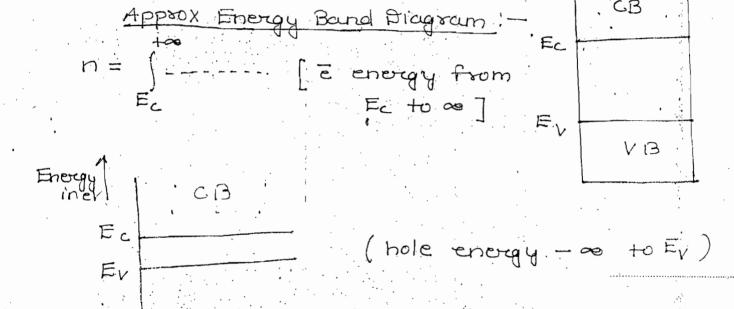

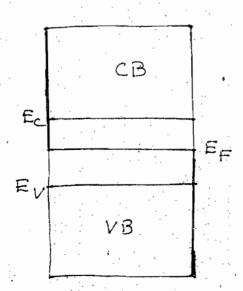

Exact Energy Band Diagram! -

- -> Ec min energy of the conduction bound of the edge of the conduction bound

- The max energy of the valence band or energy at the edge of valence band.

- The energy possessed by free & will be in the trange of (Ec to a)

The conc of  $\bar{\epsilon}$  in the conduction bound is given by  $n = N_c e^{-(\bar{E}_c - \bar{E}_F)}/kT$

08

where  $E_F = Fermi energy in eV$   $N_C = material constant and is a function of temperature$

$$N_{c} = 2 \left( \frac{2\pi K T m_{n}}{h^{2}} \right)^{3/2}$$

$$N_{c} = 2 \left( \frac{2\pi R}{h^{2}} \frac{m_{n}}{h^{2}} \right)^{3/2} + 3/2$$

where h = Planck's constant = 6.64 × 10-34 Jsec

If T=300, then

Nc =

orduction band

mn = effective mass of &

Effective mass of the E is the mass of e in the given material when E is revolving in its orbit

For Si  $\frac{m_n}{m} = 1.08 = > m_n = 1.08 m$

$=> m_n = 1.08 \times 9.1 \times 10^{-31} \text{ kg}$  rest mass of  $==> 1.08 \times 9.1 \times 10^{-31} \text{ kg}$  (9.1 × 10-31 kg)

mass of E i.e. [mn > m] i.e. 8% greater

Concentration of hold in valence barral:

The energy possessed by holes in valence bar is in the range of (- as to + Ev)

The conc of hole in the valence band is  $P = N_V \mathcal{E}^{-(E_F - E_V)}/kT$

a function of temperature NOTE:

NV is approxima

- ely equal to

density of

ostates in

Valency band

$N_V = 2 \left( \frac{2\pi K Tmp}{h^2} \right)^{3/2}$   $= 2 \left( \frac{2\pi K mp}{h^2} \right)^{3/2} T^{3/2}$

=>  $N_V = -\frac{3}{2}$

If T=300k, then

$\Rightarrow$   $N_V =$

mp = effective mans of hole

Fox Si

$\left(\frac{mp}{m}\right) = 0.56$  =>  $mp = 0.56 \frac{m}{m}$  TE mass of proton (1.6 × 10<sup>-27</sup> kg)

$mp = 0.56 \times 1.6 \times 10^{-27}$ =  $0.896 \times 10^{-27} \text{ kg}$

#### NOTE: -

٩

(8)

٩

٩

(3)

(3)

(3)

- 1. Effective mass of electron is greater than the rest mass of electron i.e. mn>m

- 2. If mo=mp then Nc=Nv

- 3. Effective mass of hole is greater than effecti mass of E.

# Derive an equation for intrinsic concentration no:-

In a semiconductor

$$P = N_V \epsilon_{\rm F}^{-(E_F - E_V)}/kT$$

— (II)

$$\Rightarrow$$

$np = N_c N_V e^{-\left[E_c - E_V\right]}$

$$= > n_i^2 = N_c N_V e^{-E_{GI/kT}} - (111)$$

but

$$N_c = 2 \left( \frac{2 \pi K T m_n}{h^2} \right)^{3/2}$$

$$N_V = 2 \cdot \left( \frac{2 \pi R Tmp}{R^2} \right)^{3/2}$$

=>

$$N_{c} \times N_{v} = 4 \left(\frac{2\pi K}{h^{2}}\right)^{3} \left(m_{n} m_{p}\right)^{3/2} - 73$$

Let

$$4\left(\frac{2\pi R}{h^2}\right)^3 \left(m_n m_p\right)^{3/2} = A_0$$

then

$$=> N_c N_V = A_0 T^3 - (IV)$$

Substitute eq-(IV) in eq-(III)

$$n_i = \sqrt{A_0} T^{3/2} e^{-FG_1/2kT}$$

# Formi Energy (EF) ! -

Formi energy in defined as the maximum energy possessed by the E at OK

Fermi energy is defined as the maximu winetic energy possessed by a cut ox

Formi Energy = Max K.E

$$\Rightarrow$$

$E_F = \frac{1}{2} m v_{max}^2$

where  $m = \text{vest mass of } \epsilon$   $= 9.1 \times 10^{-3.1} \text{ kg}$

$$\Rightarrow \sqrt{2F_F} m_{1S}$$

It is the equation for velocity of E terms of fermi energy:

OR

Fermi energy is also defined as the energy possessed by fastest moving E at OK.

# Fermi-Dirac Function! - f(E)!-

-> It is also called as fermi-dirac probability function.

→ f(E) indicate the probability E existing as a function of E

For metal or semiconductor

$$(E)$$

$$f(E) = \frac{1}{1 + E^{(E-E)}/kT}$$

where E = Energy possessed by the Einel

(1)

$$E > E_F$$

,  $f(E) = \frac{1}{1 + e^{+\infty}} = \frac{1}{1 + \infty} = 0$

This indicates no  $\bar{\epsilon}$  are available in the semiconductor with energies  $\bar{\epsilon} > \bar{\epsilon}_F$  Since the probability answer is 10.

(11)

$$E < E_F$$

,  $f(E) = \frac{1}{1 + e^{-20}} = \frac{1}{1 + 0} = 1$

Since probability is 1 it indicates at T=0K, E'S are available in the semiconductor with energies  $E < E_F$

$$A+T \neq OKT>OK:-$$

If  $E=E_E$ ,  $f(E)=\frac{1}{1+e^o}=\frac{1}{2}$  or 0.5 or 50/

- -> Fermi level is the characteristic level with 50% probability of being filled, if no forbidden band exists.

- -> In metal probability of @ existing is 1 or loop

- The semiconductor if the probability of a existing is f(E) then probability of hole existing in the semiconductor is [-f(E)]

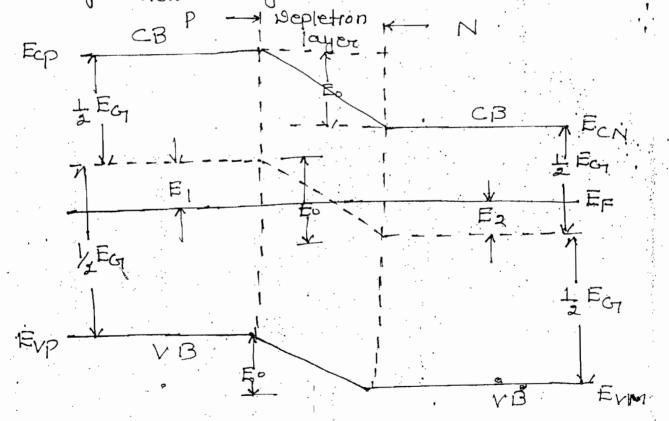

# Fermi Level in intrinsic semiconductor:

In intrinsic semiconductor

$$=> N_c \varepsilon^{-(E_c-E_F)/kT} = N_v \varepsilon^{-(E_F-E_v)/kT}$$

$$= > \frac{N_{c}}{N_{v}} = e^{-\frac{E_{F} + E_{v} + E_{c} - E_{F}}{KT}}$$

$$\Rightarrow \frac{\log N_c}{N_v} = \frac{E_c + E_v - 2E_F}{kT}$$

$$E_c + E_V - 2E_F = kT \log_e \frac{N_c}{N_V}$$

$$= \sum_{k=1}^{\infty} \frac{E_c + E_V}{2} - \frac{kT}{2} \log_e \frac{N_c}{N_V}$$

In intrinsic semiconductor, formi level dependently on temperature

Couse-(1):-

Let

$$m_n = m_p$$

then  $N_c = N_V$

$$\Rightarrow \log_e \frac{N_c}{N_V} = 0$$

$$\Rightarrow E_F = E_c + E_V$$

(8)

(3)

٩

(3)

٨

(8)

(#)

(

Ę)

(<u>;</u>

٩

The fermi level now existing exactly at the centre of energy gap

Cause-(11):

$$A+ T=0K$$

$$E_F = E_c + E_V$$

In intrinsic semiconductor at OK, ferm level is existing exactly at the centre of energy gap.

MOTE! -

In intrinsic semiconductor, fermi level will be existing exactly at the centre of the energy gap under the following conditions:

$$(1)$$

$m_n = m_p$

Couse-(111):-

Let T = 300K

where T=, 300K

In intrinsic semiconductor at room temperatures, the fermi level will be passing through the centre of the energy gap.

Slightly above the centre of the energy gp]

At room temperature because of thermal energy a no of covalent bond will be broken and equal no of E & holes are created and there will be a small conductivity in the semiconductor.

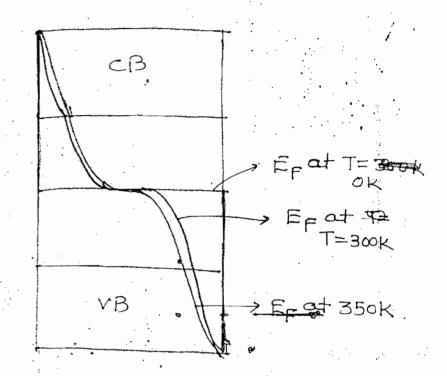

Case - (1V) !-

Position of formi level in intrinsic semi--conductor at different temperature:

#### Lecture - 4

Fermi level in n-type enemiconductor .-

(\*)

(33)

**(B)**

(3)

(1)

ુ:)

٠

٩

(\*)

٧

(3)

$$=> \frac{N_c}{N_c} = e^{(E_c - E_F)/kT}$$

=> · loge

$$\frac{Nc}{Np} = \frac{E_c - E_F}{kT}$$

$$= > E_c - E_F = kT log \frac{N_c}{ND}$$

It indicates the position of fermi level below the conduction band

In n-type esemiconductor, fermi level is a function of temperature and doping conc

CB

Let

$$T = OK$$

$$\Rightarrow \boxed{E_F = E_C}$$

of conduction band  $E_V$ - Donor energy level is always rewret to conduction band as VBcompare to centre

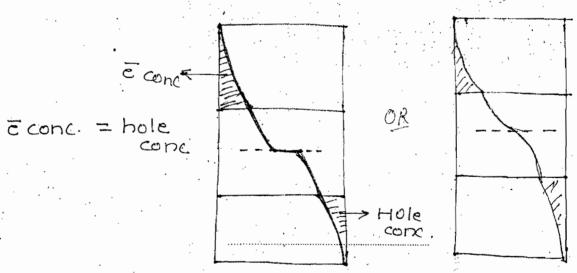

At room temperculaire, in in-type servico-- inductor, feremit level exist just below the donor energy level > In n-type esemiconductor as temperature increases from OK CB to 300K at some intermediate E temperature, the fermi-level will be considering with the  $E_V$ donor energy level. ÝВ AE & hole conc. Econc. e conc >> Hole Conc Pifferent: → Shape of E 8 conc. Hole conc. are possible acc. to your choice at 7=300K Density of states pensity of states in CB Ar almost equal Density of States in VB Diagramatic Representation CB. of both E, hole conc. 8 Ec £,9 Fermi level ĒF E > Hole VB Conc.

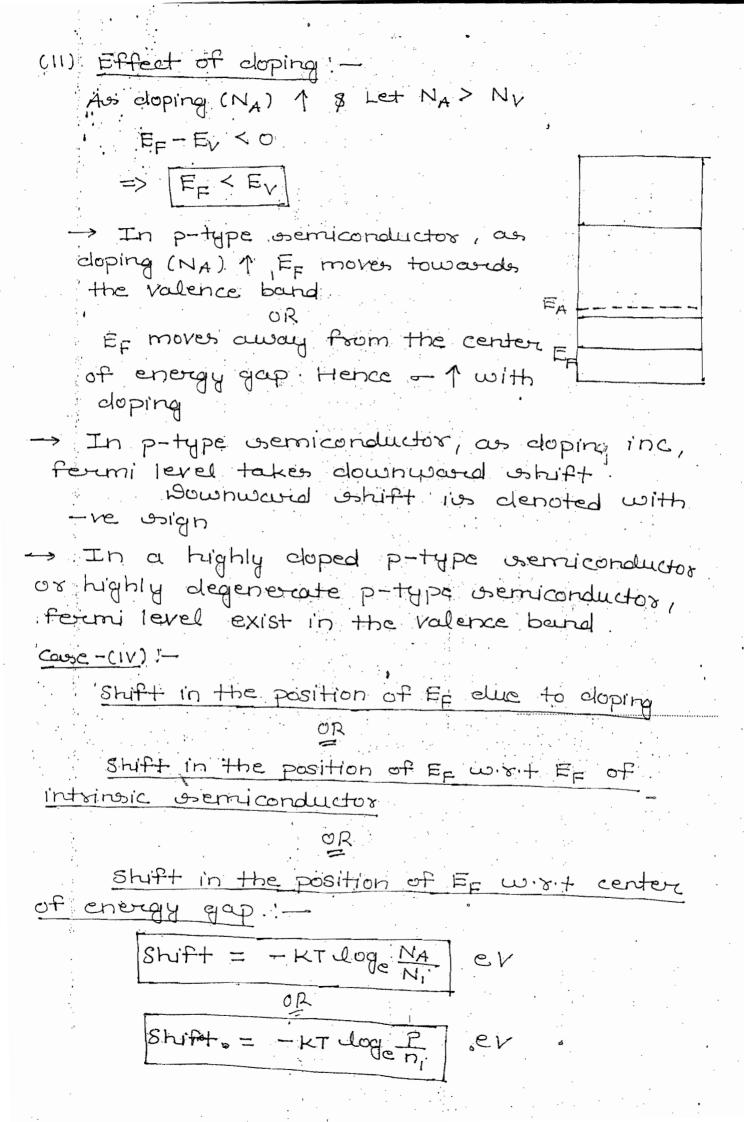

(11) Effect of Boping!

Aus doping (No) 1

S Let No > No

٩

(4)

<u>.</u>

(کی)

۹

(

٠٤)

(1)

(E)

٤

۱

ᅠ૱.

EC-EF (O, =) [EC < EF

- In N-Type semiconductor, as doping (NB) 1

EF moves towards conduction band or EF moves

away from the center of energy gap Hence

1 with doping

- -> In N-type isemiconductor as doping increases, formi level takes upward shift

- In a highly doped esemiconductor or highly degenerate n-type esemiconductor fermi level will be in the conduction bound

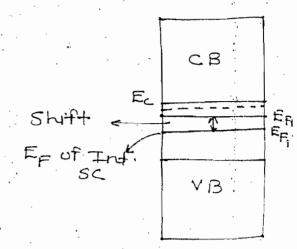

Coose-(IV):-

Shift in the position of fermi level due to doping! -

Shift in the position of Ep wist Ep of intrinsic osemiconductor:

Shift in the position of FF wist center of energy igap:

\*\* Shift = KT loge

$$\frac{n}{n_i}$$

| eV

Cane-(V)!-

<u>(23)</u>

(1)

Docivation for Shift! -

Shift = EFN-EF

But EFN = Ec - KT loge No

8 EF; = Ec+EV - KT log Nc/NV

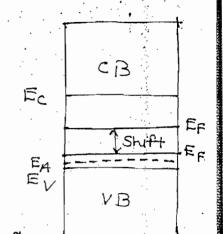

Fermi Level in P-Type semiconductor: -

$$P \approx N_A$$

$$= > \frac{N_Y}{N_A} = e^{(E_F - E_V)/KT}$$

$$\Rightarrow$$

$log_e \frac{N_V}{N_A} = \frac{E_F - E_V}{KT}$

It indicates the position of fermi level above the valence band in the p-type semiconductor

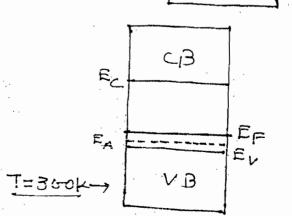

In p-type semiconductor, fermi level is a function of temperature and coping conc.

where T = 300K.

-> In p-type semiconductor at room temperatur formi level exist just above the acceptor energy level. Density of states E & hole conc. Density of estates in , Density of Holeconc estates in Hole conc >> E conc Courc - (111) ! -Mathexmatical Analysis: -Ep-Ev = KT loge NV Effect of temperature: -As temp 1, NV 1 (T>300K) 3 Let NV>NA EF-EV >0  $\Rightarrow$   $E_F > E_V$ EF CH In p-type esemicorductor, as temp I Ex moves away from valence band Ex moves towards the center of energy gap. Hence - I with temperative In p-type semiconductor, the position of formi level for different temperature 13 given above

٠

٩

٨

(3)

66)

(\*\*\*)

<del>(11)</del>

...)

**3**

(3)

(\*)

Couse-CV):

Shift = EFP Fi

But EFP = Ev + KT loge NV

8 FF: = Fc+FV - KT loge Nc 2 2 2 NV

NOTE !-

To the p-type semiconductor, at curve temperature, the fermi level will be at the center of energy gap and the conductivity will become minimum and also the p-type semiconductor will become intrinsic semiconductor

aues: In an n-type semiconductor, the fermi level lies 0.3 eV below conduction band at 300k, if the tempt is increased to 330. Find the approx new position of fermi level.

Soln: N-Type SC Ec-EF = KT Loge NC No

Since No value in not given and cannot be found the variation of No with the temperature in neglected and therefore

Ec & EF, & T => 0.3eV & 300 - (1) Fc-FF & 330 - (11)

$E_{c}-E_{F}=\frac{330}{360}\times0.38V=0.338V$

Delow the conduction band if the conc. of donor atoms is doubled find the new position of fermi level.

Assume KT = 0.03eV

Soln: - No = No e-(Ec-EF)/KT

$N_D = N_C e^{-0.4/0.03} - (1)$

$2N_{B} = N_{C} e^{-(E_{C}-E_{F})}$  (11)

$\frac{1}{z} = \frac{e^{-0.4/0.03}}{e^{-(E_c - E_F)/0.03}}$

$$= \frac{1}{2} = \frac{-0.4}{0.03} + \frac{E_c - E_{F_2}}{0.03}$$

$$= \frac{1}{2} = \frac{-0.4}{0.03} + \frac{E_c - E_{F_2}}{0.03}$$

$$= \frac{1}{2} = \frac{-0.4}{0.03} + \frac{E_c - E_{F_2}}{0.03}$$

$$= \frac{1}{2} = \frac{-0.4}{0.03} + \frac{1}{2} = \frac{1}{2}$$

٩

**\***

٩

(1)

= 0.379 ev , Ans

above the valence band, if the conc. of acceptor above the valence band, if the conc. of acceptor atoms is increased by 3 times. Find the new position of fermi level Assume KT = 0.03eV

Ans = 0.367eV

aues: - In a SC at scoom temperature, the intrinsic carreione conc and intrinsic resolutivity are 1.5 x 1016 /cm3 and 2x10130m respectively. it is converted an extrinsic isemiconductor with a doping conc. of 1020/m3. Find the whift in formilevel due to doping Shift = KT loge Doping conc. ev Soln:-= 8.62 × 10-5 (300) loge 1020 eV = 0.227 cV, Ans ones - Si i'm doped with Boson cong of 4x 10 atoms /cm3 Assume n; = 1.5 x 10 /cm3, T = 27°C compare to undoped si, the formitevel of doped sisoin! -Shift = -KT loge Nai ev = -8.62 x 10-5 x 300 x log 4x1017 = -0.442 eV , Ans. Downward Shift = -0.442 eV Hown is hift of 0.442 eV Ques! - A Si SC i'm doped with donor impurities with ocesultant doping profile n=Groc & n>>ni, sample is espaced isolated. Find the built in electric field as a function of oc

Also calculate field at  $x = 1 \mu m$  at room tempt. Soln: The esemiconductor is in-type and  $\bar{e}$  current density  $\bar{J}_n = \bar{J}_n (\beta_i f_i) + \bar{J}_n (\beta_n f_i)$

= Vondn + nqunE

Sample is isolated.  $J_n = 0$   $h = G_1 \times$

$\frac{dn}{dx} = G_1$

$$0 = G_{1}x_{1}u_{1}E_{0} + q_{1}B_{1}G_{1}$$

$$\Rightarrow x u_{1}E_{0} = -B_{1}$$

$$\Rightarrow E_{0} = -\frac{B_{1}}{u_{1}x_{1}} \quad but \quad \frac{B_{1}}{u_{1}} = V_{1}$$

$$\Rightarrow U_{1}E_{0} = V_{1}E_{0}$$

$$= \frac{V_T}{x}$$

Equation for built in electric field as a functi of x

(11)

$$x = 1 \mu m$$

At room tempt,  $V_7 = 26 m V$

$$\mathcal{E} = -\frac{\lambda^{\perp}}{\lambda}$$

$$=$$

$\frac{26 \times 10^{-3} \text{ V}}{1 \times 10^{-6} \text{ m}}$   $=$   $\frac{26 \times 10^{-3} \text{ V}}{1 \times 10^{-6} \text{ m}}$

# WORKBOOK - 1

|         | MOKKDOOK - 1                            |

|---------|-----------------------------------------|

| 13. 8   | 24                                      |

| 14 A, C | ~Bcst 25                                |

| 15 A    | 26                                      |

| 16 B    | 27                                      |

| N7 B    | 28                                      |

| 18 B    | 29                                      |

| 19 C    | 30                                      |

| 20 .B   |                                         |

|         | 14 A, C<br>15 A<br>16 B<br>17 B<br>18 B |

12 23

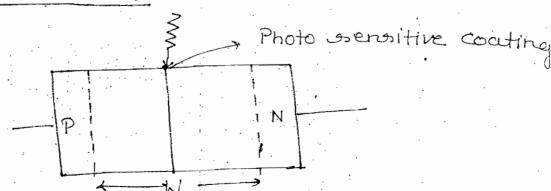

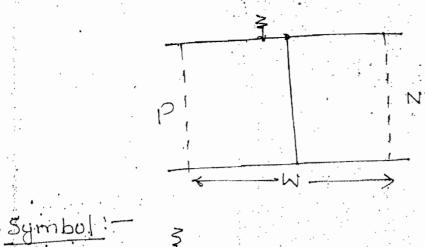

#### Hall Effect !-

8

3

( )

٩

$(\cdot,\cdot)$

٩

٨

٩

3

٩

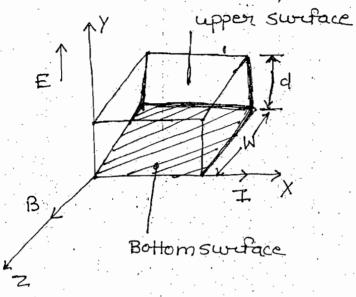

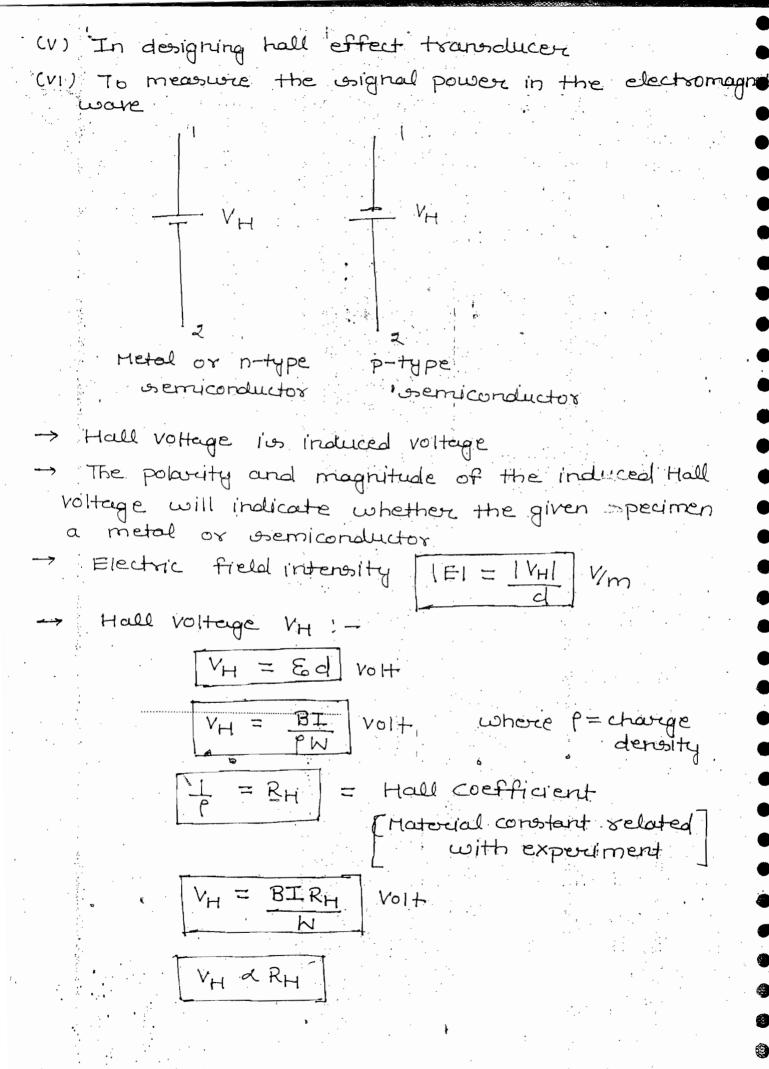

It istates that if a ispecimen (metal or Sc. carrying the current I is placed in transverse field magnetic field B, an electric field intensity E is induce in a direction perpendicular to both 'B' and 'I'

- -> The specimen must be either equal ox square or rectangular in shape

- -> " is the width of specimen

- blu the bottom oswerace and upper swerace of the ospecimen

- The awarent is taken on X-direction and magnetic field in the Z-direction and field intensity will be in Y-direction

In the above diagram, the direction of the force is downward and direction will be same for and hole because hole is physically not existing and hole is basically a valence e

- -> From the above experiment we can determine

- (1) Whether the given especiment is metal or semiconductor

- (11) To measure the covorier conc.

- (III) mobility of charge cavalers

- (IV) Magnetic flux density

-> From Hall experiment

<u>π = 8 </u> σ RH

where - = conductivity of especimen

×× TI ≈ 4 KH

## Application:

(1) Magnet-o-field meter or magnetic field meter

#### NOTE :-

**3**

9

**3**

- (1) Magnetic field meter is an instrument working on the principle of Hall effect and is used in the measurement of magnetic flux density B.

- (11) From the hall experiment we can measure magnetic flux density and magnetic field intensity (HAB)

- (III) Hall effect multiplier is instrument which has two i/p "i.e. (i) curvert (II.) magnetic flux density and induced Hall voltage is the product of I & B.

Hall effect multiplier is an instrument in which one i/p signal is applied in the form of current and another i/p signal is applied in the form of magnetic flux density and Hall voltage is the product of the two i/p signal and hence the name multiplier

- (IV) In Hall effect multiplier, the two i/p osignal are multiplied.

- (V). If the polarity of Hall voltage is the for the bottom surface, the given especimen is p-type (VI) Hall voltage is measured with to appear surface of especimen.

In metal  $V_H = -ve$ In n-type esemiconductor,  $V_H = -ve$ In p-type  $v_H = +ve$ For intrinsic esemiconductor,  $v_H = 0$

charge density (P) = charge x carrier conc. ] c/m

Hall coefficient (RH):-

PH = 1 = 1 m3/C

In metal & n-type semiconductor  $R_H = -ve$ In p-type isemiconductor,  $R_H = tve$ In intrinsic isemiconductor  $R_H$  is very large.

In intrinsic isemiconductor converge conc. are

In intrinsic semiconductor covorier conc are very large small and therefore Hall coefficient will be very large.

=> RH = 4

Since VH & RH

VH ~ \_L

-> In metal o- 1'05 very large, VH is small (UV)

The semiconductor or is small, VH is large (mV or ascound (Volt)

semiconductor

NOTE !-

(3)

٩

۹

**₩**

(4)

(3)

6

٩

<u>ښ</u>

٩

٩

٨

٩

(1) In extrinsic esemiconductor, RH is independent of temperature.

$$R_{H} = \frac{1}{\sqrt{x} \text{ couvrier conc.}}$$

In extrinsic semiconductor consister consimean majority consister cons and it is independent of temperature Hence RH is independent of temperature

$$R_{H} = \frac{V_{H} W}{BT}$$

Since all parameter are constant Hence Hall coefficient is independent of temperature.

$$R_{H} = \frac{U}{\sigma} \qquad T \wedge U \vee V$$

$$\downarrow R_{H} \uparrow = \frac{U}{\sigma} \downarrow V$$

In intrinsic semiconductor, Hall coefficient decreases with temperature

In intrinsic semiconductor cavarier conc. increase with temperature and hence RH decrease with temperature

Hence RH i'vs decrease with tempercuture

#### NOTE !-

- The mobility of charge coverier can be experi--mentally found by using Hall effect.

- 2. The mobility of charge carrier can be found by using Hayness Schockley experiment.

- 3. By using Hayness-Schockley experiment we can measure

- (a) mobility of minority coveres

- (b) Diffusion constant of the minority covoriers

cours: - A doped semiconductor especimen RH=36×10<sup>1</sup> m<sup>3</sup>/c and ecesiestivity 9× 10<sup>-3</sup> m achieving single coverier conduction the mobility and density of charge coverier in especimen approximately are given by —

$$501^{01}$$

- (1)  $R_{H} = 3.6 \times 10^{-4}$

$p = 9 \times 10^{-3} \Omega m$

$u = P$

$u = -R_{H}$

$$=\frac{1}{9 \times 10^{-3}} \times 3.6 \times 10^{-4} = 0.04$$

coverer conc = coverer density

```

Assuming single coveres conduction

= coverier conc. x q x u

=> convier density = 5

=> coverier conc =

Resistivity X9 X LL

ours! - Find the magnetic field in a ocedarquelar

especimen having 4 mm width and 2mm thick with

a Hall coefficient 10-3 m3/c and aucrent of ImA

is passed through the isample. Hall voltage 2mv

1'es obterined

VH = 2m W= 4m el= 2 (Frestiguel

Soln! -

they convert

R_{H} = 10^{-3}

I = IA

in m.

RH = VHW

= 8 Wb/m2 , Ans

cues: - Find the magnitude of Hall coefficient in

n-type germanium bar of width 3mm and height 2mm

Assume B = 0.9 w/m2 & I = 1.5 mA

Soln:-

\omega = 3mm = 3 \times 10^{-3} m

b = 2mm = 2 \times 10^{-3} m

VH = BI => VH = RHBID

R_H = V_H \times W

\Rightarrow RH = 0.5 x 3 x 10<sup>-3</sup>

0.9 × 1.5 ×10-3

= 222 m3/c , Ans

```

(3)

٩

(و)

8

$( \circ )$

٨

٩

٩

$(\cdot)$

<u>(ii)</u>

⑧ .

£:)

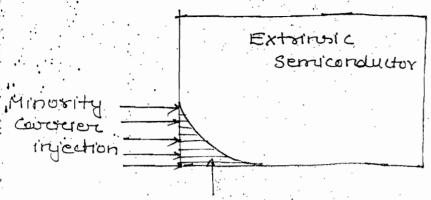

Injected minority coverer

- will be moving from higher conc. to lower conc i.e. due to property of diffusion.

- The injected minority coverient conc. will be maximum where they are introduced and conc. will be decreasing into the osemiconductor as exponential decaying function with distance.

- when holes are injected into the n-type remiconductor, the injected hole in the semi-conductor will be moving from higher cone to lawer cone i.e. the property due to diffusion.

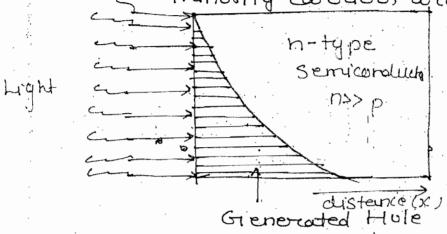

## Low level Injection!

- The means the conc. of majority carriers is fare greater than the conc. of minority carriers hight is focussed on the semiconductor only under low level injection.

- when light falls on the semiconductor because of photon energy as larger por of the surface of the semiconductor gets heated up and due to the thermal energy a large no of covalent bonds are broken and equal no of

electrons and holes are created. Under esteady estate Analysis:

٠

(

1

()

( )

(3)

٨

()

...)

۹

Excess & conc. = excess hole conc.

-> Since majority carrier conc in semiconductor is almost independent of temperature. When light falls on the semiconductor minority carriers are generated.

The generation rate for the generation of minority conscients in the n-type isemiconductor is

dt = excess hole generated

minority carrier life time

$$\Rightarrow \frac{\Box P}{\Box E} = \frac{\triangle P}{\Box P}$$

Unit for generation rate -> e-hole pair/cm3

Cours: - 1 esemiconductor i'es irradicated with dight esuch that the carriers are uniformly generated through out it volume. The semiconduct is n-type with No = 10<sup>19</sup>/cm<sup>3</sup>. Excess e cone. I'm esteady estate i'es an = 10<sup>15</sup>/cm<sup>3</sup> & if The 5 usec & Tp = 10 usec the generation rate due to irradication i'es.

Soln: - AP = An = 10<sup>15</sup>/cm<sup>3</sup>

$$\frac{dp}{dt} \cdot = \frac{\Delta p}{Cp}$$

=

$$\frac{10^{15}}{10 \times 10^{-16}}$$

=  $10^{20}$  e hole pair'/cm<sup>3</sup>

/sec, An

and Cp = 10 usec. 1's \_\_\_\_\_

$$\frac{dP}{dt} = \frac{\Delta P}{C_P} = \frac{10^{15}}{10 \times 10^{-6}} = 10^{15 + 5} = 10^{10}$$

when light falls on the semiconductor & hole pair / cm3/sec

on the sourface where the light is focussed & the hole conc. exponentially electroners into the elepth of the semiconductor

-> When the light falls on the n-type semiconductor there will be two coverent component

(1) Hole diffusion current because of light falling on the n-type esemiconductor

(11) Hole daft awarent

in the n-type esemiconductor which introduces built in electric field.

- uctor, Hole diffusion convert (Ip)>> Ip (diff)>>> Ip (diff)>>> Ip (driff)

-> When light falls on n-type, the convert is mainly due to hole diffusion convert.

-> Under low level injection in the semiconductor, current is dominated by diffusion current

٩

(3)

٠

(4)

۹

(3)

(3)

3

-> When light falls on n-type osemicorductor under low level injection

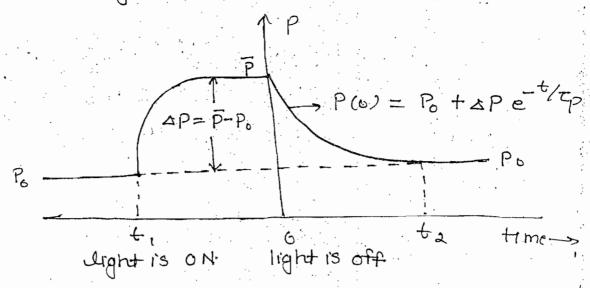

$$P(\mathbf{t}) = P_0 + \Delta P e^{-t/\tau}$$

$$A + t = 0$$

$$\Rightarrow P(0) = P_0 + \Delta P e^{-t/\tau}$$

$$\Rightarrow P(0) = P_0 + \Delta P X I$$

$$\Rightarrow P(0) = P_0 + \Delta P X I$$

At time

$$t = t_2$$

where  $t_2 = 57p$

$$P(t_2) = P_0 + \Delta P_c^{-5}$$

$$= > P(t_2) = P_0$$

-> When eight falls on the n-type semiconducto

$$P = AP = AP = AP$$

when light falls on the N-type, holes are generated and hole conc. is maximum where the light is focused at x=0

If

$$x=0$$

then  $P(0) = \Delta P e^{-x}/p$

$\Rightarrow P(0) = \Delta P \Rightarrow Excess hole generated$

ar exponential decrease in function into the osemiconductor.

$$A + DC = Lp$$

$$P(0) = \Delta p e^{-1}$$

$$= > P(0) = \Delta p$$

It indicates the length of diffusion is defined as the length into the semiconductor where the excess generated conc. will reduced to 1 of its peak value.

If

$$DC = 5Lp$$

.

=>  $P(0) = \Delta p e^{-5}$

=>  $\Delta p = 0$   $P(0) = 0$

## Lecture 90

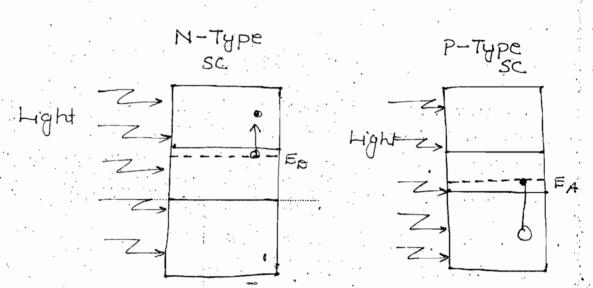

#### Intrinsic Excitation: -

- electron may be exciting from valence bained to conduction band and it is called intrinsic excitation

- -> For intrisic excitation photon energy >  $E_{G_7}$ ->  $hv > E_{G_7}$

٩

٩

٨

required must be equal to its energy gap For Extrinsic Excitation! -

- -> When light falls on n-type isemiconductor, an electron may be excited from donar energy level into the conduction band and it is called extrinsic excitation

- when light falls on p-type semiconductor, an electron may be excited from valence band into acceptor energy level (EA) and it is called extrinsic excitation

- required in older for the, obser for si

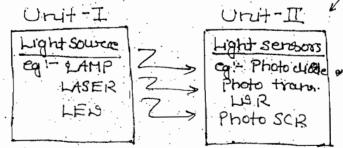

# Photoconductive Effect! -

-> The process where the conductivity of a semi-- conductor material or device increases with

the light falling on it is called photoconduct . - ive effect

- -> Photochode, phototransiostor will be working on the principle of photoconductive effect

- -> The process where resistivity of a material or device decreases with the light falling on it is called photoresistive effect.

- -> LAR operates on the principle of photo-- resistive effect

# Classification of semiconductors! -

- (1) Direct bound gap semiconductor.

- (11) Indirect band gap esemiconductor

# Direct Band Grap Semiconductor Indirect Band Grap Semi-

1. During recombination most of energy will be released in the form of light eg: GaAs (Best example)

- Gan, Grasb, zns, other IMAS, Cds, InP example Insb, cdse

Highly unstable Property,

unveliable 2. Most of the free & will be directly falling from conduction band to valence band & energy is directly released by falling e's in the form of light

# Conductor

awing recombination most of the energy will be released in the form of

eg! - Si & Gre (Best example)

other - ALP, AlAs, Pbs, example Pbse, Grap Highly curestable

Most of the free E falling from conduction band will go to the intermediate level & then tell into the valence band & chergy is dissipated in the form of heat.

## Direct Band Group SC

3. The falling & will be directly releasing the energy & hence the name direct bandgap semiconductor

4. During the ocecombination most of the falling E from conduction band will be directly falling into the valence" band and energy is dissipated in the form of light and at the same time very few & from the conduction band when falling will be colloiding with the Crystal and these crystal will absorb the energy from the falling e and heated up and they will release some energy in the form of heat

9

()

(:)

5. The energy of falling & changes i.e. K.E & P.E changes

P.E inc & K.E dec.

6. The direction of the falling E will not change (direction means from to CB to VB)

7. No change in the path of falling E

Indirect BandGrap SC The falling & will be indirectly releasing the energy through the crystal in the form of heat & hence the name indirect bandgap semi--conductor Dwing recombination most of free E falling from the conduction band will be colloiding with the crystal & these crystals will be absorbing the energy from the falling & \$ gets heated up and they released energy in the form of heat but very few falling & from conduction band will be escaping the collision & they will fall directly into the valence band and small energy is released in the form of light The energy of falling & changes i.e. K.E.S.P.F both changes.

Direction of falling e will not charge

The path of falling & charges (due to intexmediate energy level or collision)

# Direct Band Grap SC

8. The energy can be released by the falling in momentum or the momentum of the falling & does not change

Momentum = mass x Velocity

Momentum is constant because there is a change in the mass of falling E along with the change in the velocity.

9. Relatively esmaller carriere lifetime

NOTE :-

InP -> Birect bandgap

GIAP -> firect bandgap gemiconductor

Indirect Band Grap SC

The momentum of the falling e charges or energy counnot be released without a charge in the momentum in the falling e

The change in.

momentum is due to

a change in the velocity

of falling E.

Relatively larger covorier

NOTE! -

InP-> Indirect bound

Grap Semiconductor

of LED because it is a indirect bandgap semiconductor

burdgap semiconductor

aues: - SC lasses are fabricated with COT BBG SC with longe T. (b) 11 11 11 smaller T CC) IBBG111 11 larger T (d) 11 11 ismaller T Ques! - Grats is an example for (1) BBG SC (11) IBG SC (111) Wide Band orap SC (11) Navrow Band Gap SC out of these correct istatement is (a) Only (1) (b) (1) & (11) (cc) (11) & (11) (d) (1) & (1 clues: - A p-type esemiconductor follows the equation P = K [ 1-x]/cm3 for 0 < x < L where k= 1015, L= 15 mm., 19p = 10 cm²/sec Jp (diff.).  $\frac{Soln}{-} - P = K \left[ 1 - \frac{3C}{L} \right]$  $\frac{dP}{dx} = -K$  $J_P(diff.) = -1 lip dP$  $= -1.6 \times 10^{-19} \times 10 \left[ \frac{-10^{15}}{15 \times 10^{-4}} \right]$ = 1.06 A/cm2 oues! - In the sc sample, if the hole conc.  $p(x) = 10^{15} e^{-x/1}p cm^{-3}$  for  $x \ge 0$  and e conc.  $p(x) = (x 10^{14} e^{-x/1}n cm^{-3})$  for  $x \ge 0$ . Lp = 4.8 x 10-4 cm , Ln = 9.6 x 10-4 cm 19p = 20 cm²/sec, Dn = 35 cm²/sec. Total current density at x=0 is \_\_ ?

(#)

**(3)**

(ij)

(1)

٩

٠

(E)

Soln -

$$J = J_n (diff) + J_p (diff)$$

=  $J_n (diff) + J_p (diff)$

=  $J_n$

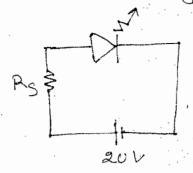

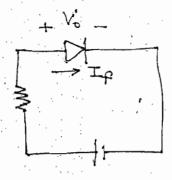

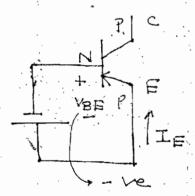

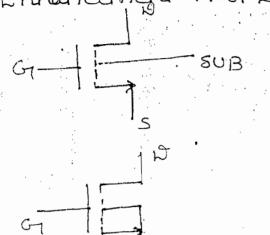

## SEMICONPUCTOR DIOBE

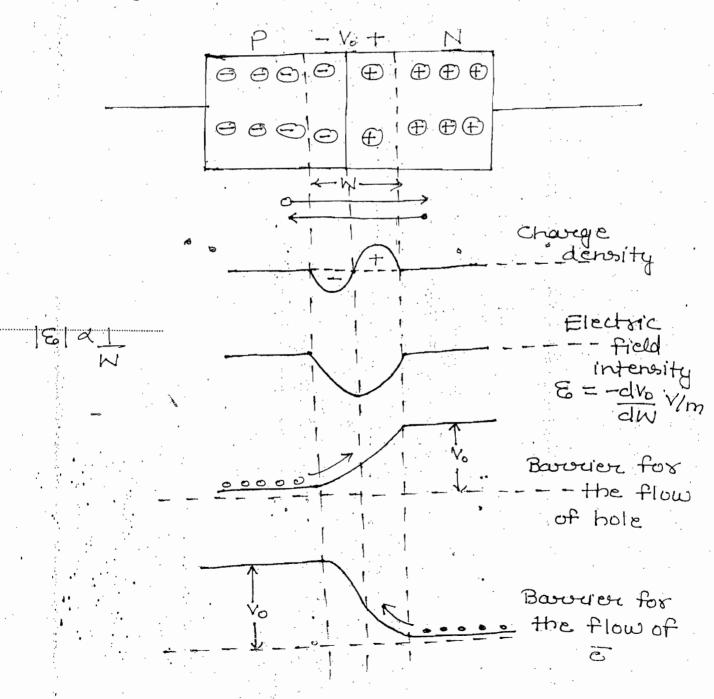

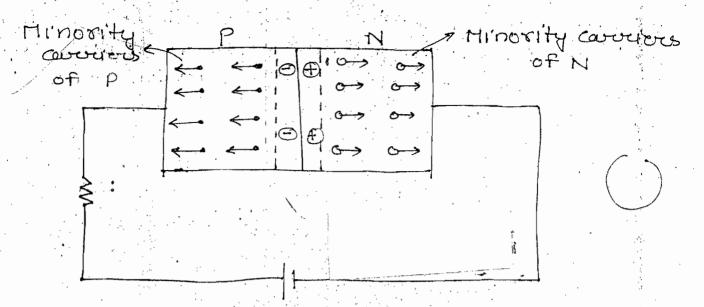

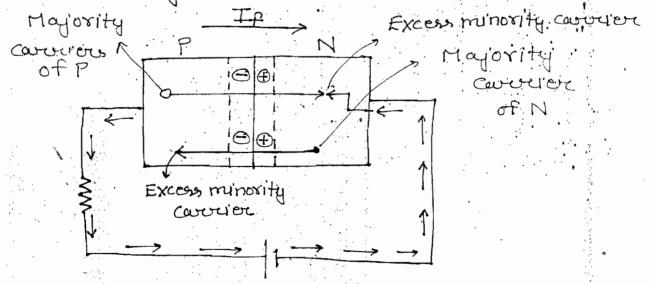

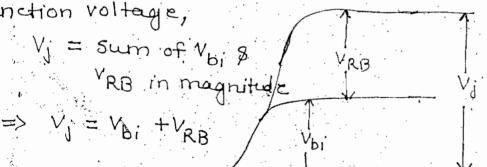

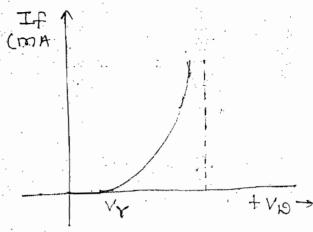

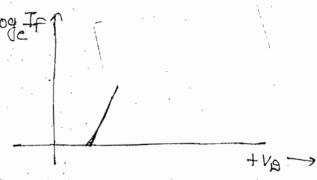

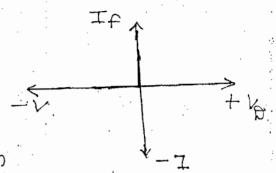

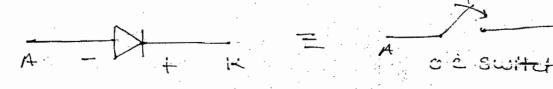

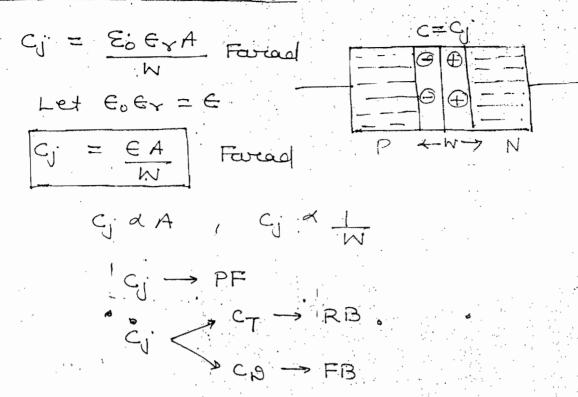

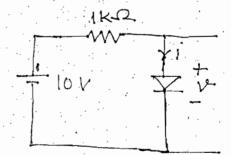

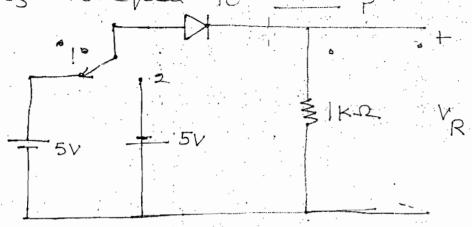

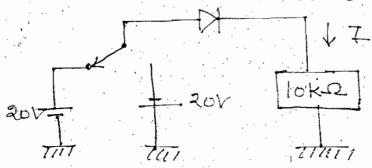

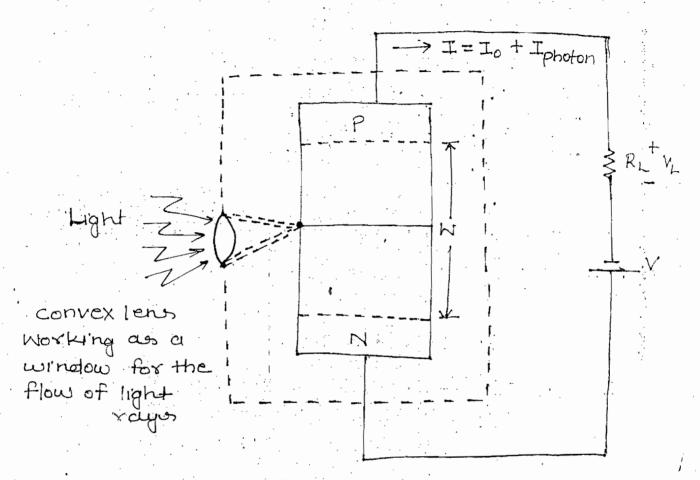

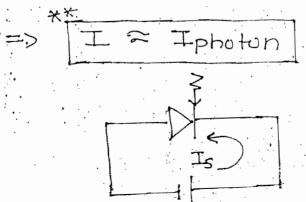

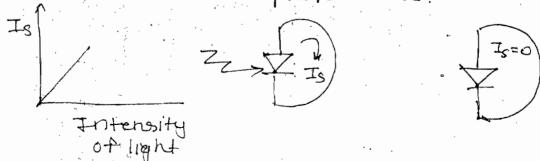

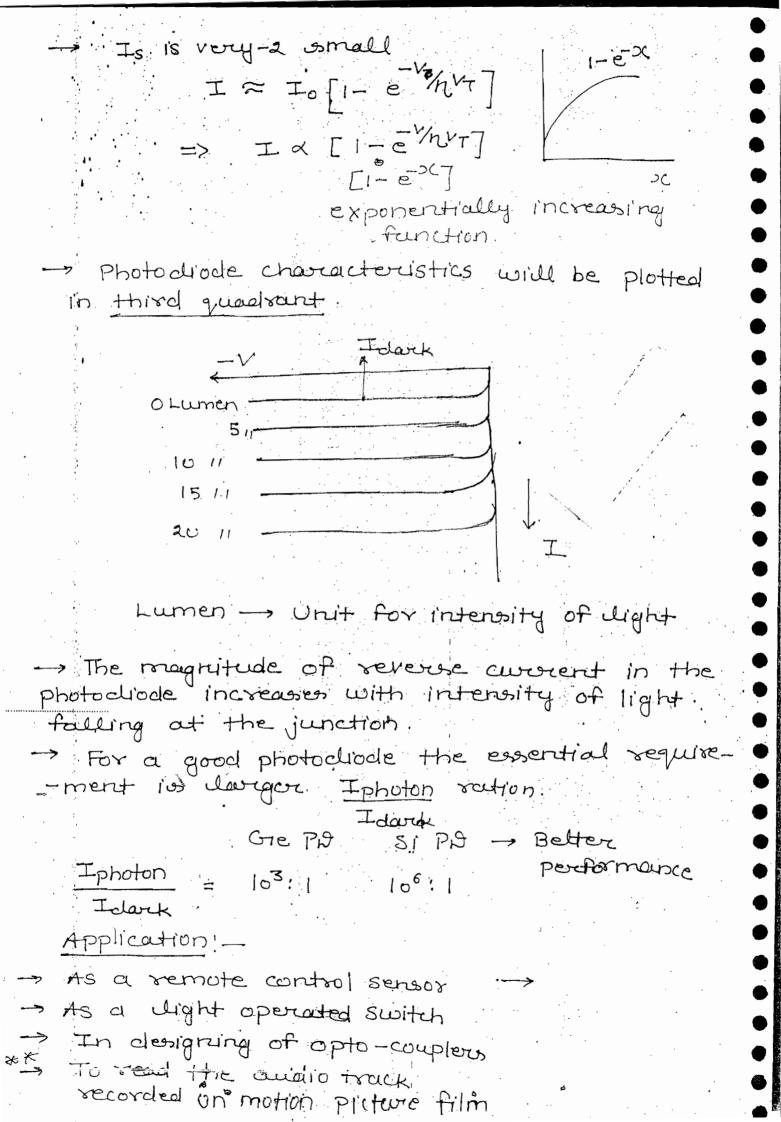

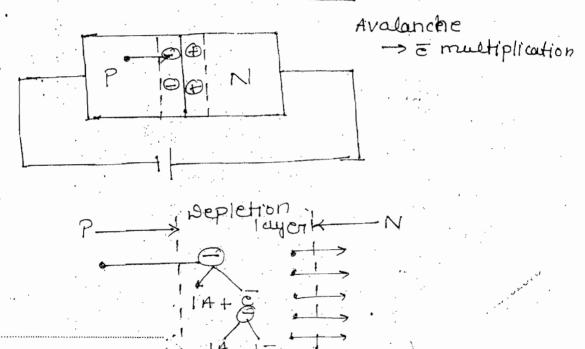

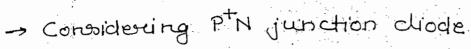

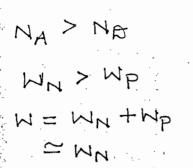

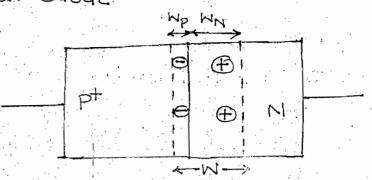

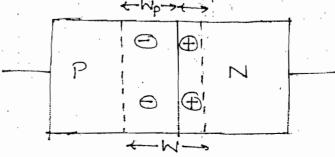

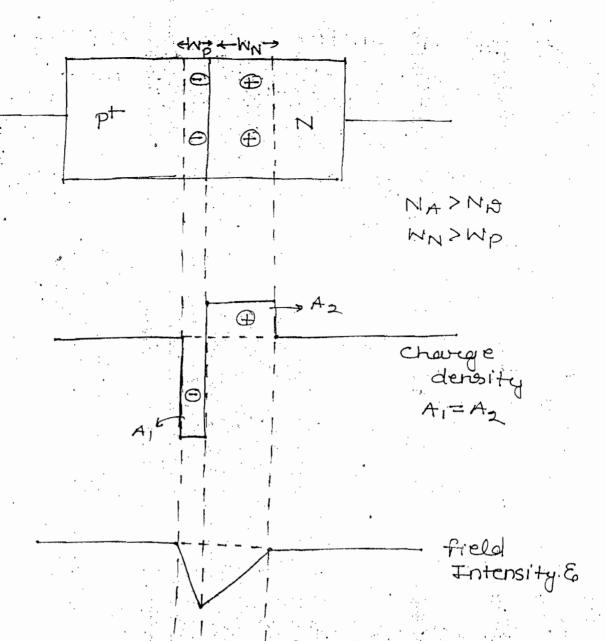

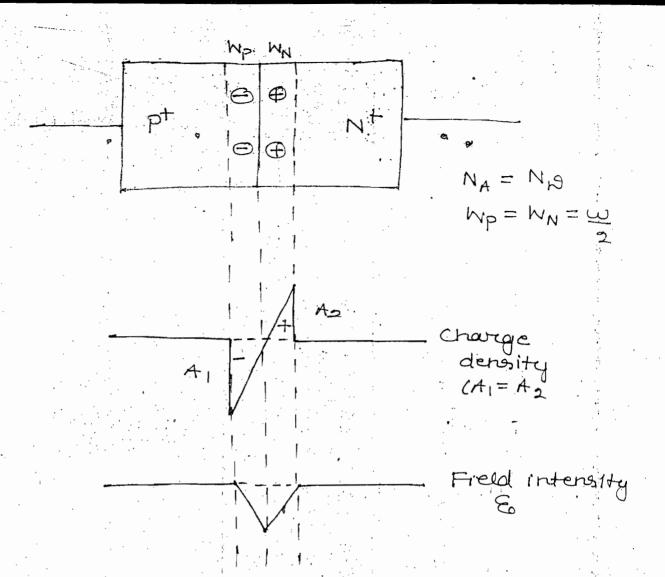

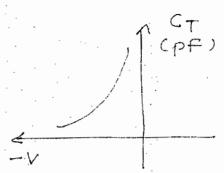

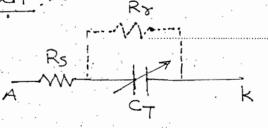

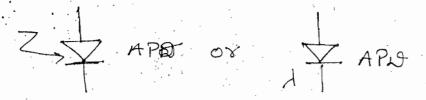

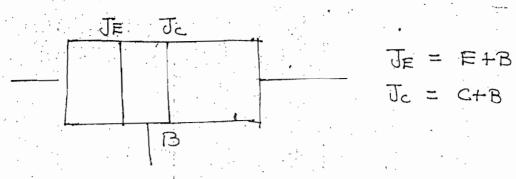

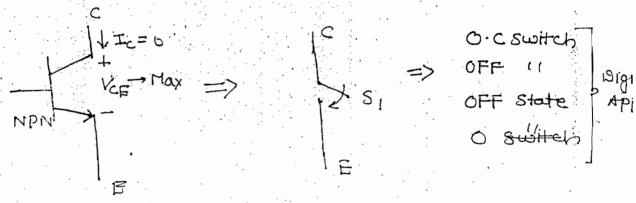

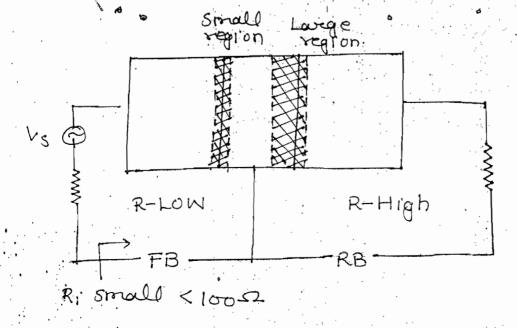

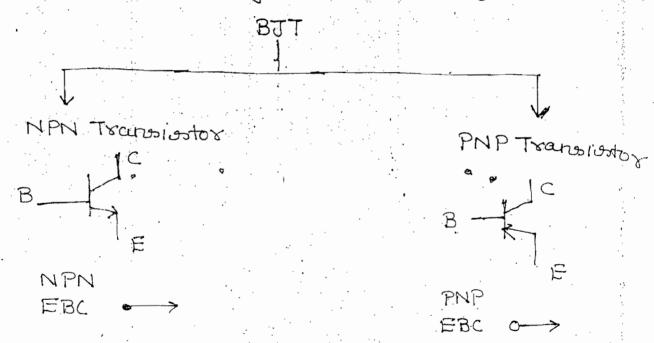

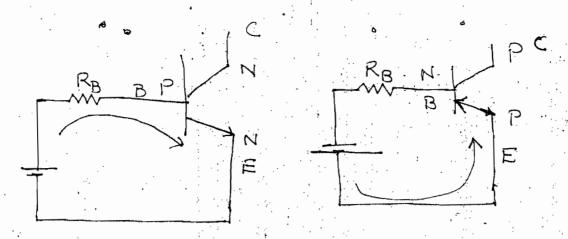

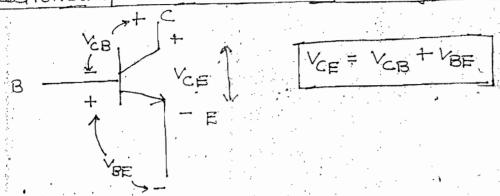

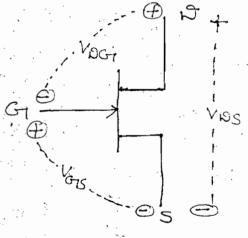

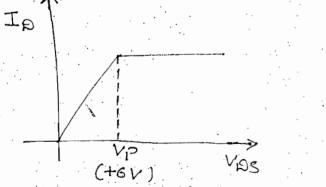

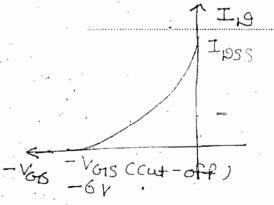

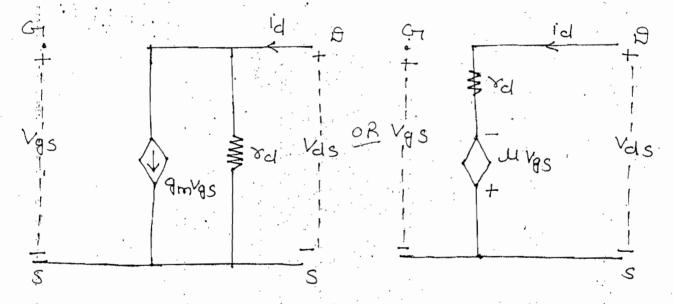

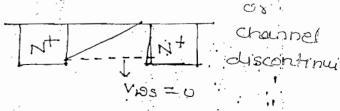

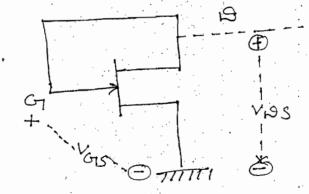

Metal SC Junction diade PN Junction Diode Metal Sc PN-, No rectification Rectification property Property exist. connot work as can work as a a rectifier rectifier eq!-(1) Point contact diode (11) Schottky diade PN Junction cliede or Junction Theory! --> PN Junction can be formed only when a bonding force is created b/w p-type & n-type sc -> Latest dioder are fabricated with any one of the following methods: -Alloy-junction Technique Diffusion CIII (III) GINUWN . (IV) Epitaxial Method -> Latest method Open Circuit PN Junction diode !-Vo = Barrior Voltage 012 Potential Hill OR. Diffusion voltage Vo = contact potential kill bobbleter

built in voltage

₩

۹

٨

۱

٨

3

٩

(3)

(3)

Typical value = 0.2V

$\rightarrow$  For Si cliode ,  $V_0 = 0.6V$  to 0.9VTypical value = 0.7V

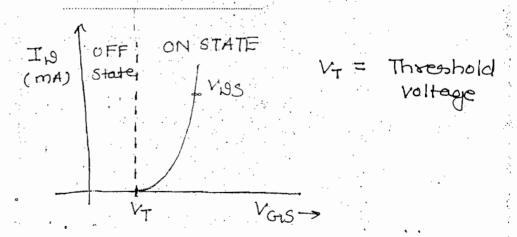

Oues: - Why biasing is applied to SC device?

Ans: - As food is available for us, biasing is necessary for semiconductor device. As biasing is applied majority charge carriers cross barrier & contribute to conductivity. Temperature is not sufficient to cross carrier across the barrier.

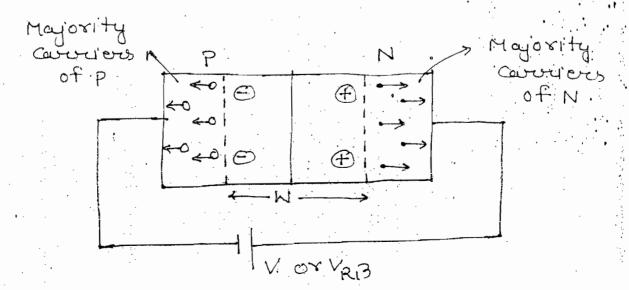

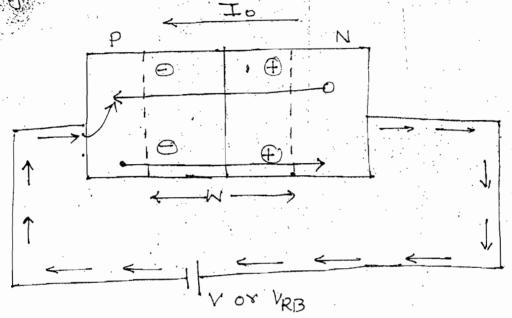

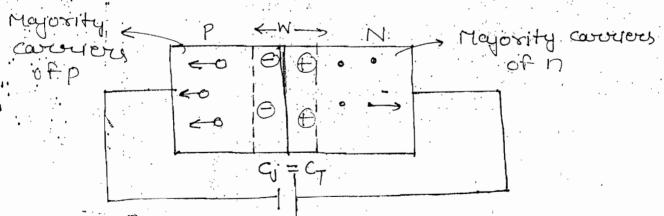

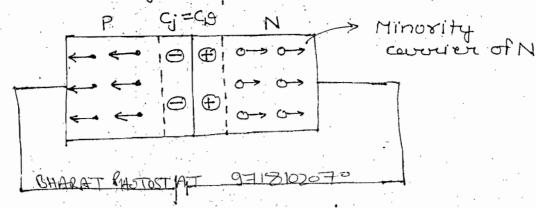

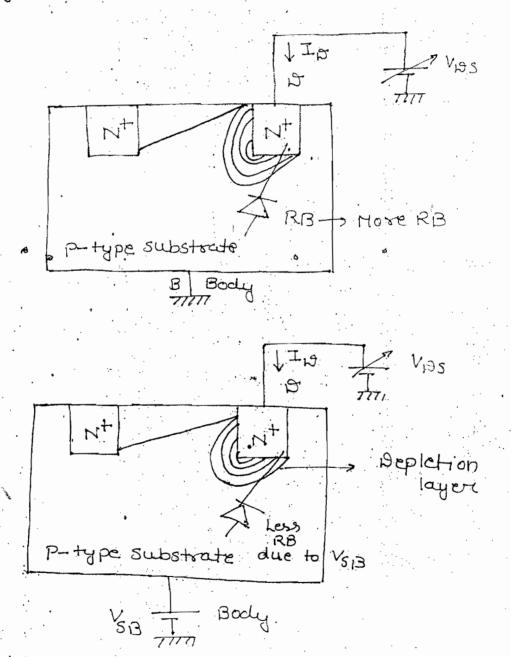

- -> Depletion layer is also called space charge oregion or transition region

- -> In the depletion layer; mobile charge carrier are zero

- of majority conviews across the junction

- -> Depletion layer opposes majority caveriers in crossing the junction

- -> Depletion layer will not oppose in crossing the junction

6.

٧

(3)

٨

(3)

(

٩

(%)

٧

;;;)

(ن)

- in crossing the junction.

- -> Depletion layer consistes of immobile charges particles (ions)

- of ions and covalent bonds

- -> Depletion layer consists of negative charges and positive charge on either side of junction

- (acceptor ions) on the p-side and positive ions. (donor ions) on the N-side

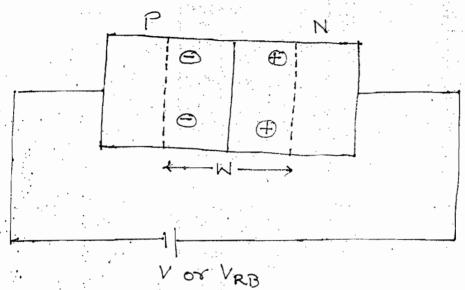

- The width of the depletion layer Wal

W=011um to 1um & typical value =0.5.un Vo is called contact potential or potential hill or barrier voltage or diffusion voltage or

built in voltage [Vbi]

For Gre diode Vo = 0.11 to 0.51 For si diode Vo = 0.61 to 0.91

Typical value = 0.2V

Typical value = 0.71

- -> The polarity of diffusion voltage is -ve to the p-side and positive towards N-side

- -> contact potential of the clicale cannot be practically measured by using a voltmeter

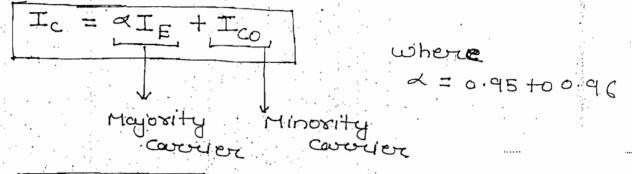

- -> In any type of PN junction, field intensity is always maximum at the junction